## 相关文档

PT 官方:

《PT32L00x 数据手册》 《PT32F00x 数据手册》

ARM 官方:

《Cortex™-M0 技术参考手册》

下载地址: https://developer.arm.com/documentation/ddi0432/c

《Cortex-M0 设备通用用户指南》

下载地址: https://developer.arm.com/documentation/dui0497/a

《ARM 调试接口架构规范 V5》

下载地址: https://developer.arm.com/documentation/ihi0031/f

《ARM CoreSight 技术参考手册》

下载地址: https://developer.arm.com/documentation/ddi0486/b

《ARMv6-M 架构参考手册》

下载地址: https://developer.arm.com/documentation/ddi0419/e

开发工具官方:

《CMSIS-Core (Cortex-M) Version 5.5.0》

下载地址: https://www.keil.com/pack/doc/cmsis/Core/html/index.html

# 目录

| 相关文档  | <b>型</b>                    | 1  |

|-------|-----------------------------|----|

| 目录    |                             | 1  |

| 文中的约  | 宿写                          | 12 |

| 寄存    | 字器描述表中使用的缩写列表               | 12 |

| 1 存储器 | 器和总线构架                      | 13 |

| 1.1   | 系统构架                        | 13 |

|       | 1.1.1 系统总线                  | 14 |

|       | 1.1.2 AHB/APB 桥(APB)        | 14 |

| 1.2   | 存储器组织                       | 15 |

| 1.3   | 嵌入式 SRAM                    | 17 |

| 1.4   | 嵌入式 Flash 闪存                | 17 |

| 1.5   | 启动配置                        | 17 |

| 2 CRC |                             | 18 |

| 2.1   | 综述                          | 18 |

| 2.2   | 特性                          | 18 |

| 2.3   | CRC 功能描述                    | 19 |

|       | 2.3.1 多项式                   | 19 |

|       | 2.3.2 种子(初始值)               | 20 |

|       | 2.3.3 反转功能                  | 20 |

| 2.4   | 寄存器描述                       | 21 |

|       | 2.4.1 CRC 控制寄存器(CRC_CR)     | 21 |

|       | 2.4.2 CRC 种子寄存器(CRC_SEED)   | 22 |

|       | 2.4.3 CRC 多项式寄存器(CRC_POLY)  | 22 |

|       | 2.4.4 CRC 数据输入寄存器(CRC_DIN)  | 23 |

|       | 2.4.5 CRC 数据输出寄存器(CRC_DOUT) | 23 |

|       | 2.4.6 寄存器列表                 | 24 |

| 3 电源挡 | 空制(PWR)                     | 25 |

| 3.1   | 综述                          | 25 |

| 3.2   | 特性                          | 25 |

| 3.3   | 电源调节器                       | 26 |

|       | 3.3.1 电源调节器                 | 26 |

|       | 3.3.2 电源复位条件                | 27 |

|       | 3.3.3 可编程的电源电压监测器(PVD)      | 27 |

| 3.4   | 低功耗模式                       | 28 |

|       | 3.4.1 进入低功耗模式               | 28 |

|       | 3.4.2 睡眠状态                  | 28 |

|       | 3.4.3 深度睡眠状态                | 29 |

|       | 3.4.4 唤醒方式                  | 29 |

|       | 3.4.5 唤醒时间                  | 29 |

| 3.5   | 寄存器描述                       | 31 |

|       | 3.5.1 电源电压监测器配置寄存器 PWR_PVDR | 31 |

| 3.5.2 系统控制寄存器(SCR)           | 32 |

|------------------------------|----|

| 3.5.3 寄存器列表                  | 33 |

| 4 复位和时钟控制(RCC)               | 34 |

| 4.1 综述                       | 34 |

| 4.2 特性                       | 34 |

| 4.3 复位功能描述                   | 35 |

| 4.3.1 系统复位                   | 35 |

| 4.3.1.1 NRST 引脚复位            | 35 |

| 4.3.1.2 软件复位                 | 35 |

| 4.3.1.3 PLL 复位               | 36 |

| 4.3.2 电源复位                   | 36 |

| 4.3.2.1 芯片上电/掉电复位            | 36 |

| 4.3.3 功能复位                   | 37 |

| 4.3.3.1 电源低电压复位              | 37 |

| 4.3.3.2 高级软件复位               | 37 |

| 4.4 时钟功能描述                   | 38 |

| 4.4.1 HSI 时钟                 | 39 |

| 4.4.2 LSI 时钟                 | 39 |

| 4.4.3 PLL 时钟                 | 39 |

| 4.4.4 系统时钟(SYS_CLK)选择        | 40 |

| 4.4.5 时钟安全机制                 | 40 |

| 4.4.6 看门狗时钟                  | 40 |

| 4.4.7 TIM4 时钟                | 40 |

| 4.4.8 时钟输出(MCO)              | 41 |

| 4.5 RCC 寄存器描述                | 42 |

| 4.5.1 时钟高频控制寄存器(RCC_HCR)     | 42 |

| 4.5.2 时钟低频控制寄存器(RCC_LCR)     | 42 |

| 4.5.3 时钟 PLL 控制寄存器(RCC_PCR)  | 43 |

| 4.5.4 时钟输出配置寄存器(RCC_MCOR)    | 44 |

| 4.5.5 时钟配置寄存器(RCC_CFGR)      | 45 |

| 4.5.6 复位状态寄存器 RCC_RSR        | 47 |

| 4.5.7 高级软件复位控制寄存器(RCC_HSFRR) | 48 |

| 4.5.8 复位控制寄存器 RCC_RCR        | 49 |

| 4.5.9 寄存器列表                  | 50 |

| 5 通用和复用功能 I/O(GOIO 和 AFIO)   | 51 |

| 5.1 综述                       | 51 |

| 5.2 特征                       | 51 |

| 5.3 GPIO/AFIO 功能描述           | 52 |

| 5.3.1 GPIO 输入配置              | 52 |

| 5.3.2 GPIO 输出配置              | 53 |

| 5.3.3 外部中断                   | 53 |

| 5.3.4 映射操作                   | 54 |

| 5.3.5 AFIO 复用 IO 功能功能描述      | 55 |

| 5.3.5.1 数字功能复用配置             | 55 |

| 5.3.5.2 模拟功能复用配置                         | 56 |

|------------------------------------------|----|

| 5.3.6 外设复用下的 IO 状态                       | 57 |

| 5.4 GPIO 寄存器描述                           | 58 |

| 5.4.1 端口数据寄存器(GPIOx_DR) (x=AD)           | 58 |

| 5.4.2 端口输出使能寄存器(GPIOx_OES) (x=AD)        | 59 |

| 5.4.3 端口输出失能寄存器(GPIOx_OEC) (x=AD)        | 59 |

| 5.4.4 输入上拉使能寄存器(GPIOx_PUS) (x=AD)        | 60 |

| 5.4.5 输入上拉失能寄存器(GPIOx_PUC) (x=AD)        | 60 |

| 5.4.6 输入下拉使能寄存器(GPIOx_PDS) (x=AD)        | 61 |

| 5.4.7 输入下拉失能寄存器(GPIOx_PDC) (x=AD)        | 61 |

| 5.4.8 输出开漏使能寄存器(GPIOx_ODS) (x=AD)        | 62 |

| 5.4.9 输出开漏失能寄存器(GPIOx_ODC) (x=AD)        | 62 |

| 5.4.10 输入施密特触发使能寄存器(GPIOx_CSS) (x=AD)    | 63 |

| 5.4.11 输入施密特触发失能寄存器(GPIOx_CSC) (x=AD)    | 63 |

| 5.4.12 端口低 8 位映射操作区域(GPIOx_MASKL) (x=AD) | 64 |

| 5.4.13 端口高 8 位映射操作区域(GPIOx_MASKH) (x=AD) | 64 |

| 5.4.14 寄存器列表                             | 65 |

| 5.5 AFIO 寄存器描述                           | 67 |

| 5.5.1 端口数字功能配置寄存器 0(AFIOx_AFS0) (x=AD)   | 67 |

| 5.5.2 端口数字功能配置寄存器 1(AFIOx_AFS1) (x=AD)   | 68 |

| 5.5.3 端口数字功能清除寄存器(AFIOx_AFC)(x=AD)       | 68 |

| 5.5.4 端口模拟功能使能寄存器(AFIOx_ANAS) (x=AD)     | 69 |

| 5.5.5 端口模拟功能失能寄存器(AFIOx_ANAC)(x=AD)      | 69 |

| 5.5.6 寄存器列表                              | 70 |

| 6 嵌套向量中断控制器(NVIC)                        | 71 |

| 6.1 综述                                   | 71 |

| 6.2 特性                                   | 71 |

| 6.3 中断和异常向量                              | 72 |

| 6.4 NVIC 寄存器描述                           | 74 |

| 6.4.1 系统中断使能寄存器 ISER                     | 74 |

| 6.4.2 系统中断禁止寄存器 ICER                     | 76 |

| 6.4.3 系统中断挂起设定寄存器 ISPR                   | 78 |

| 6.4.4 系统中断挂起清除寄存器 ICPR                   | 80 |

| 6.4.5 系统中断优先级寄存器 IPRx                    | 82 |

| 6.4.6 NVIC 寄存器列表                         | 83 |

| 7 外部中断控制器(EXTI)                          | 84 |

| 7.1 综述                                   | 84 |

| 7.2 特性                                   | 84 |

| 7.3 EXTI 功能描述                            | 85 |

| 7.3.1 有效的外部中断                            | 85 |

| 7.3.2 外部中断唤醒低功耗模式                        | 85 |

| 7.3.3 外部中断的配置                            | 86 |

| 7.4 EXTI 寄存器描述                           | 87 |

| 7.4.1 外部中断请求开放寄存器(EXTIx IES) (x=AD)      | 87 |

2022-02-18 第 3页,共 272 页

| 7.4.2 外部中断请求禁止寄存器(EXTIx_IEC) (x=AD)   | 87  |

|---------------------------------------|-----|

| 7.4.3 外部中断类型配置寄存器(EXTIx ITS) (x=AD)   | 88  |

| 7.4.4 外部中断类型清除寄存器(EXTIx_ITC) (x=AD)   | 88  |

| 7.4.5 外部中断双沿类型配置寄存器(EXTIx_ITDS)(x=AD) | 89  |

| 7.4.6 外部中断双沿类型清除寄存器(EXTIx_ITDC)(x=AD) | 89  |

| 7.4.7 外部中断极性配置寄存器(EXTIx_PTS) (x=AD)   | 90  |

| 7.4.8 外部中断极性清除寄存器(EXTIx_PTC) (x=AD)   | 90  |

| 7.4.9 外部中断标志寄存器(EXTIx_IF) (x=AD)      | 91  |

| 7.4.10 寄存器列表                          | 92  |

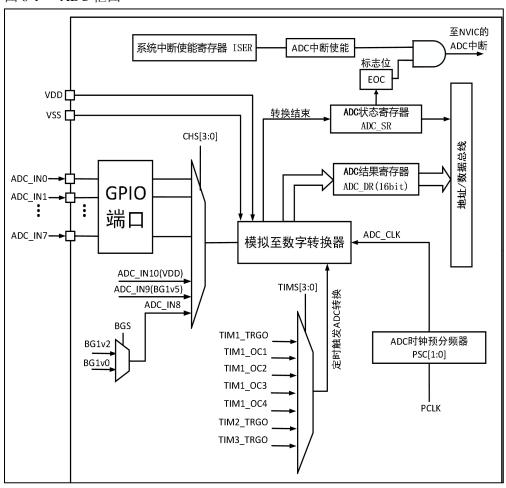

| 8 模拟/数字转换(ADC)                        | 94  |

| 8.1 综述                                | 94  |

| 8.2 特性                                | 94  |

| 8.3 功能描述                              | 95  |

| 8.3.1 ADC 开关控制                        | 96  |

| 8.3.2 ADC 时钟                          | 96  |

| 8.3.3 通道选择                            | 96  |

| 8.3.4 转换模式                            | 96  |

| 8.3.4.1 单次转换                          | 96  |

| 8.3.4.2 连续转换                          | 97  |

| 8.3.4.3 定时触发转换                        | 97  |

| 8.3.5 ADC 中断                          | 97  |

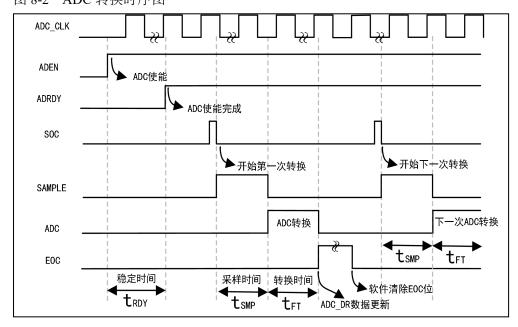

| 8.3.6 时序图                             | 98  |

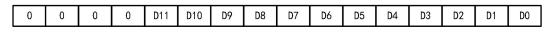

| 8.3.7 数据对齐                            | 98  |

| 8.3.8 可编程的采样时间                        | 99  |

| 8.3.9 ADC 采样转换时间                      | 99  |

| 8.4 寄存器描述                             | 100 |

| 8.4.1 ADC 控制寄存器 ADC_CR                | 100 |

| 8.4.2 ADC 状态寄存器 ADC_SR                | 102 |

| 8.4.3 ADC 结果寄存器 ADC_DR                | 102 |

| 8.4.4 ADC 采样时间寄存器 ADC_SAMPLE          | 103 |

| 8.4.5 寄存器列表                           | 104 |

| 9 高级定时器(TIM1)                         | 105 |

| 9.1 综述                                | 105 |

| 9.2 特性                                | 105 |

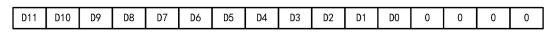

| 9.3 TIM1 功能描述                         | 106 |

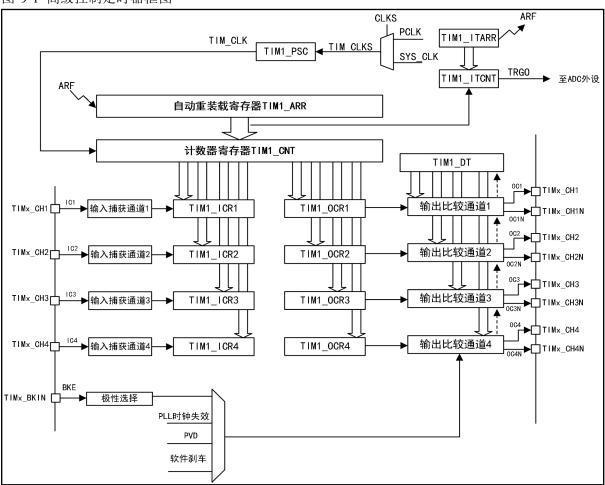

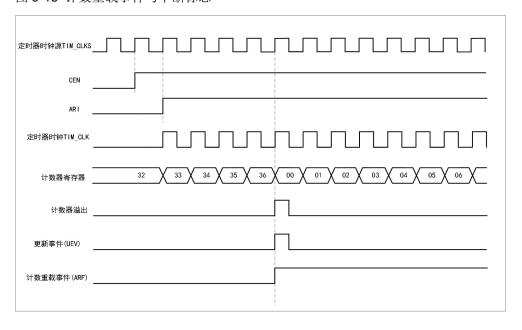

| 9.3.1 时基单元                            | 107 |

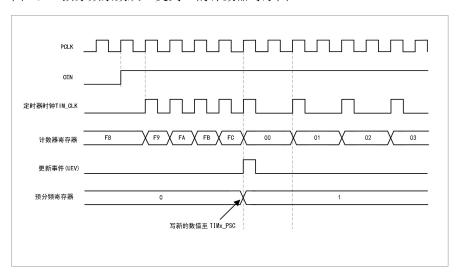

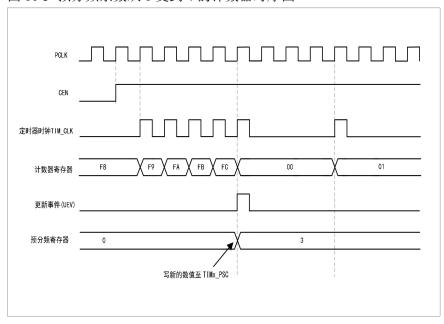

| 9.3.1.1 预分频器                          | 108 |

| 9.3.2 计数模式                            | 109 |

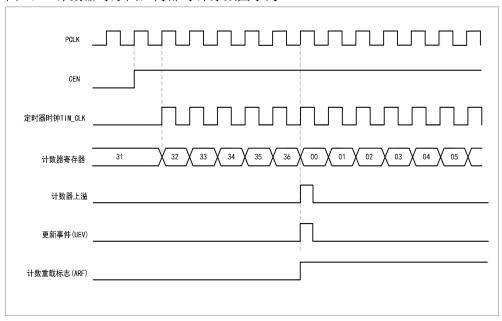

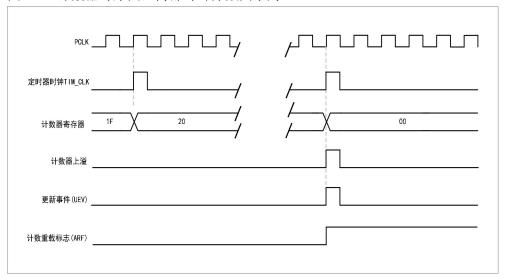

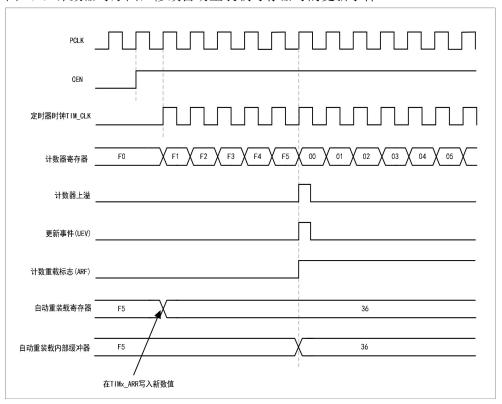

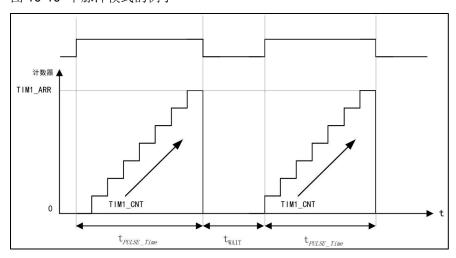

| 9.3.2.1 向上计数模式                        | 109 |

| 9.3.2.2 向下计数模式                        | 111 |

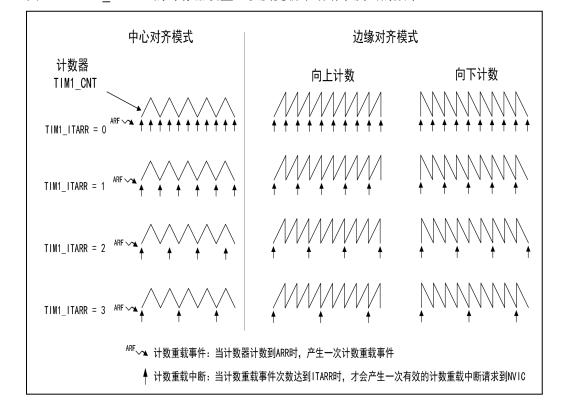

| 9.3.2.3 中央对齐模式(向上/向下计数)               | 113 |

| 9.3.2.4 单脉冲模式                         | 114 |

| 9.3.3 时钟源                             | 115 |

| 9.3.4 更新中断                            | 115 |

| 9.3.5 中断重复计数器                                   | 116 |

|-------------------------------------------------|-----|

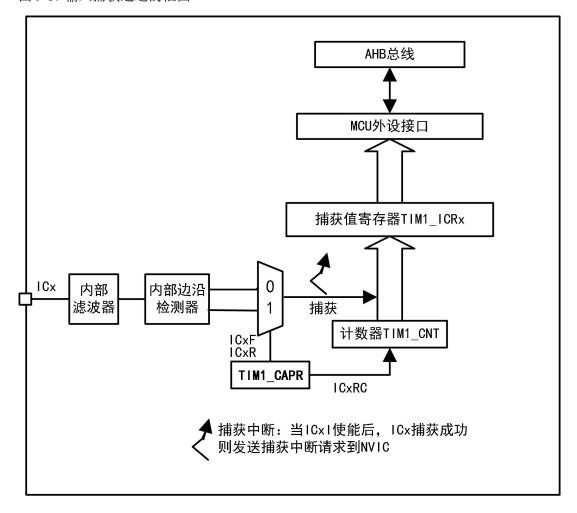

| 9.3.6 输入捕获功能                                    | 117 |

| 9.3.6.1 输入捕获通道                                  | 117 |

| 9.3.6.2 输入捕获模式                                  | 118 |

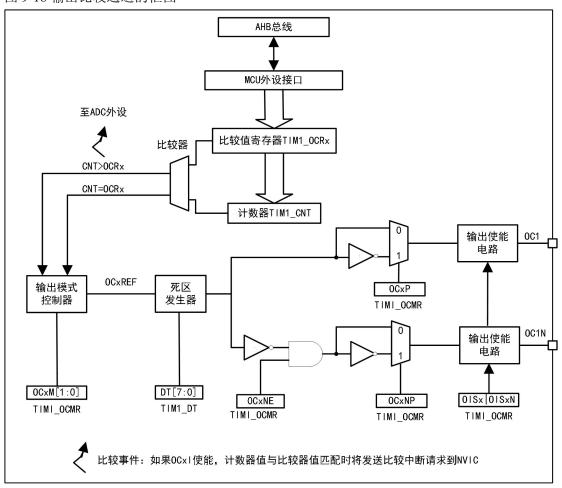

| 9.3.7 输出比较功能                                    | 119 |

| 9.3.7.1 输出比较通道                                  | 119 |

| 9.3.7.2 输出比较模式                                  | 120 |

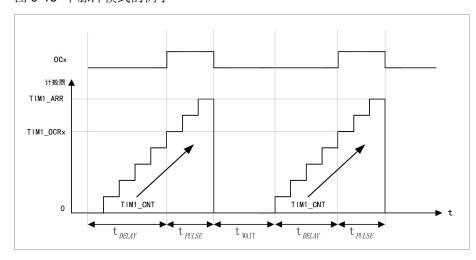

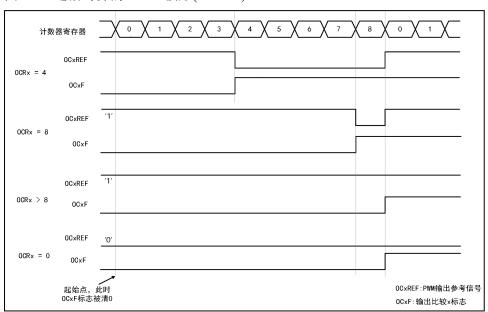

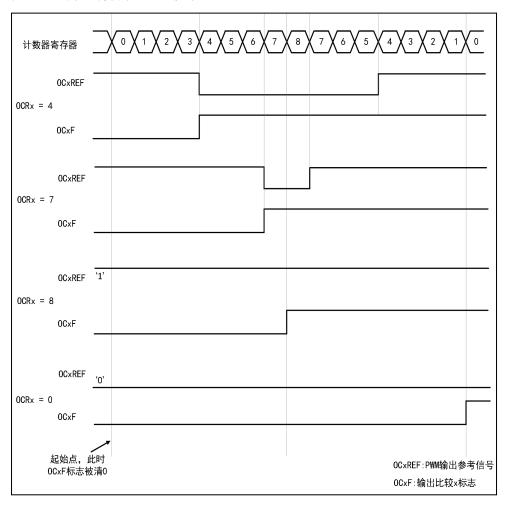

| 9.3.8 PWM 模式                                    | 121 |

| 9.3.8.1 PWM 边沿对齐模式                              | 121 |

| 9.3.8.2 PWM 中央对齐模式                              | 122 |

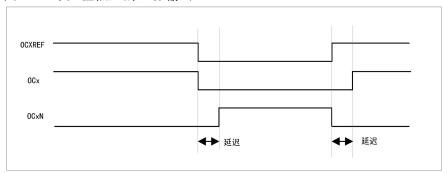

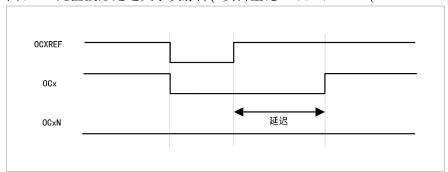

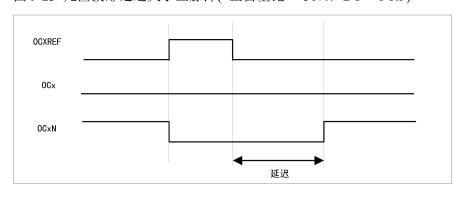

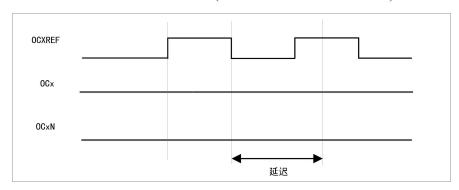

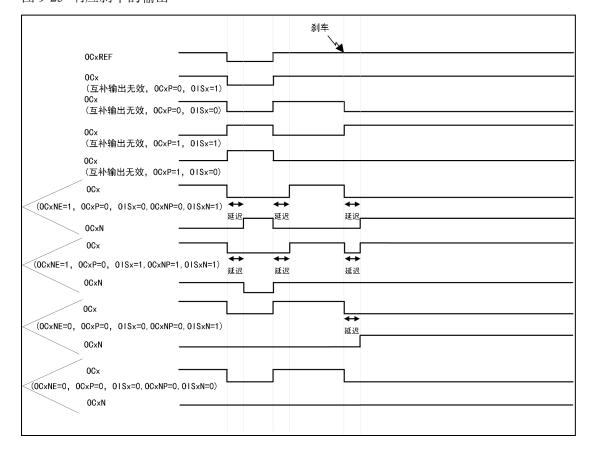

| 9.3.8.3 互补输出和死区插入                               | 123 |

| 9.3.8.4 刹车功能                                    | 125 |

| 9.3.9 外设间同步信号                                   | 126 |

| 9.3.9.1 TRGO 信号                                 | 126 |

| 9.3.9.2 OCx 事件                                  | 126 |

| 9.3.10 调试模式                                     | 126 |

| 9.4 TIM1 寄存器描述                                  | 127 |

| 9.4.1 TIM1 状态寄存器(TIM1_SR)                       | 127 |

| 9.4.2 TIM1 控制寄存器 1(TIM1_CR1)                    | 129 |

| 9.4.3 TIM1 中断重复计数值寄存器(TIM1_ITARR)               | 131 |

| 9.4.4 TIM1 中断重复计数器(TIM1_ITCNT)                  | 131 |

| 9.4.5 TIM1 预分频寄存器(TIM1_PSC)                     | 132 |

| 9.4.6 TIM1 计数器寄存器(TIM1_CNT)                     | 132 |

| 9.4.7 TIM1 控制寄存器 2 (TIM1_CR2)                   | 133 |

| 9.4.8 TIM1 自动重装载寄存器(TIM1_ARR)                   | 134 |

| 9.4.9 TIM1 输出比较值寄存器(TIM1_OCRx)(x =1, 2, 3, 4)   | 134 |

| 9.4.10 TIM1 输入捕获配置寄存器(TIM1_CAPR)                | 135 |

| 9.4.11 TIM1 输入捕获值寄存器(TIM1_ICRx)(x = 1, 2, 3, 4) | 136 |

| 9.4.12 TIM1 输出比较配置寄存器(TIM1_OCMR)                | 137 |

| 9.4.13 TIM1 死区时间控制寄存器(TIM1_DT)                  | 140 |

| 9.4.14 寄存器列表                                    | 141 |

| 10 基本定时器(TIMx)                                  | 142 |

| 10.1 综述                                         | 142 |

| 10.2 特性                                         | 142 |

| 10.3 TIMx 功能描述                                  | 143 |

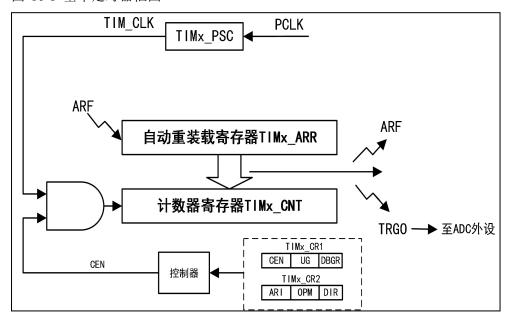

| 10.3.1 时基单元                                     | 143 |

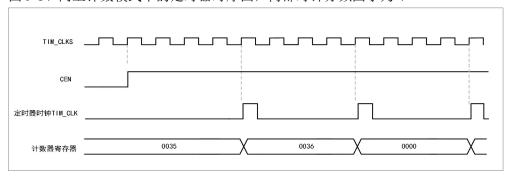

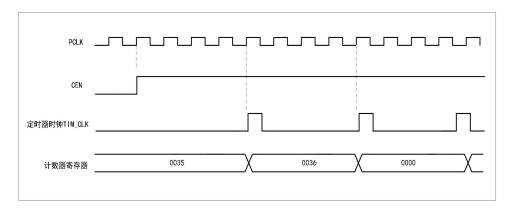

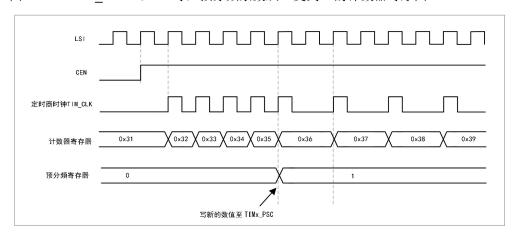

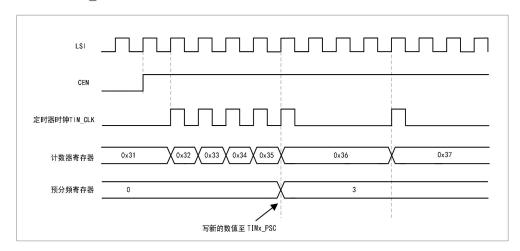

| 10.3.1.1 预分频器                                   | 144 |

| 10.3.2 计数模式                                     | 145 |

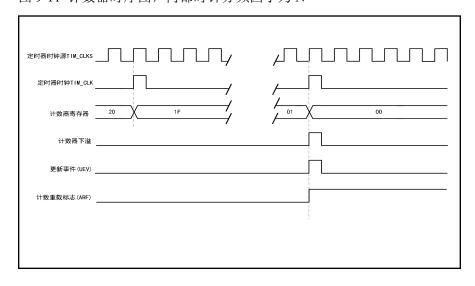

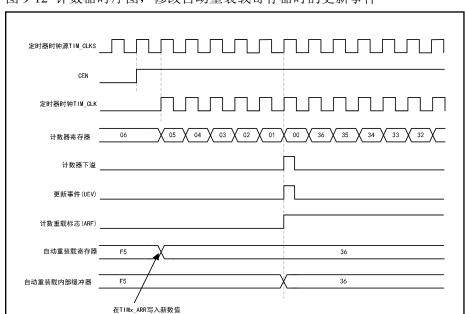

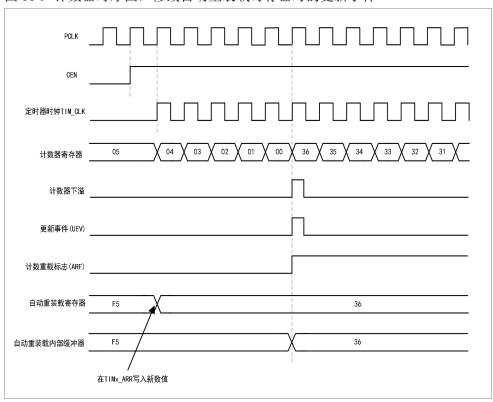

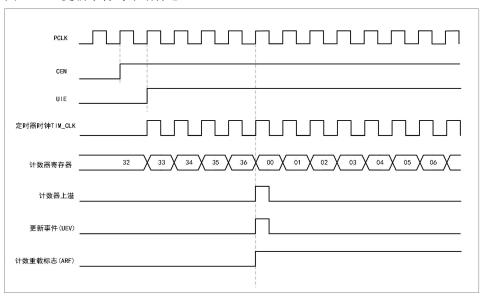

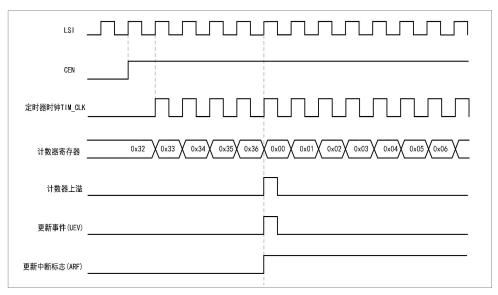

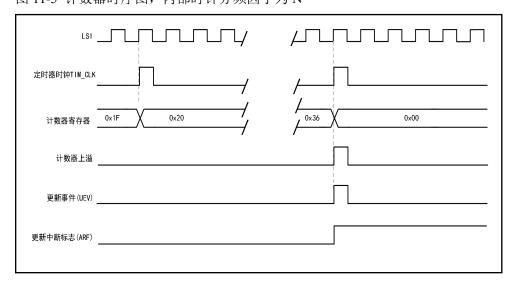

| 10.3.2.1 向上计数模式                                 | 145 |

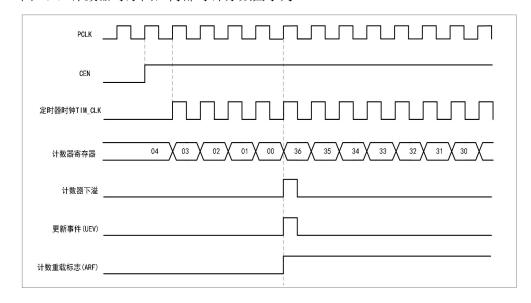

| 10.3.2.2 向下计数模式                                 | 147 |

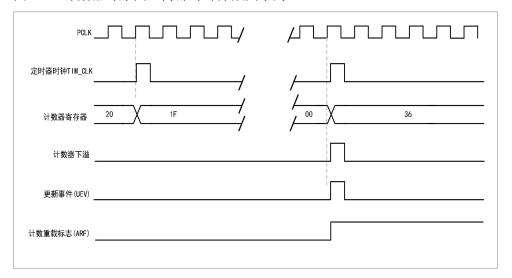

| 10.3.2.3 单脉冲模式                                  | 149 |

| 10.3.3 时钟源                                      | 149 |

| 10.3.4 更新中断                                     | 150 |

| 10.3.5 同步信号 TRGO                                | 150 |

| 10.3.6 调试模式                              | 150 |

|------------------------------------------|-----|

| 10.4 TIMx 寄存器描述                          | 151 |

| 10.4.1 TIMx 状态寄存器(TIMx SR)(x = 2, 3)     | 151 |

| 10.4.2 TIMx 控制寄存器 1(TIMx_CR1)(x = 2, 3)  | 152 |

| 10.4.3 TIMx 预分频寄存器(TIMx_PSC)(x = 2, 3)   | 153 |

| 10.4.4 TIMx 计数器寄存器(TIMx_CNT)(x=2,3)      | 153 |

| 10.4.5 TIMx 控制寄存器 2(TIMx_CR2) (x= 2, 3)  | 154 |

| 10.4.6 TIMx 自动重装载寄存器(TIMx_ARR)(x = 2, 3) | 155 |

| 10.4.7 寄存器列表                             | 156 |

| 11 低功耗定时器(TIM4)                          | 157 |

| 11.1 综述                                  | 157 |

| 11.2 特性                                  | 157 |

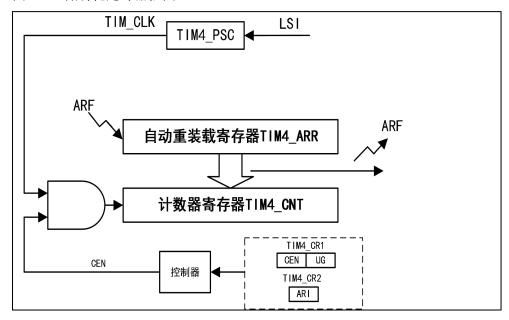

| 11.3 TIM4 功能描述                           | 158 |

| 11.3.1 时基单元                              | 158 |

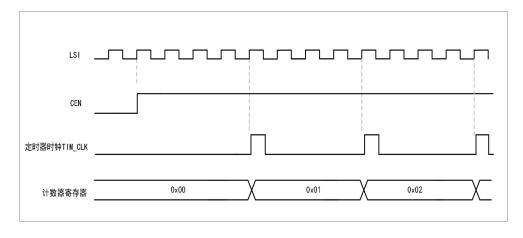

| 11.3.1.1 预分频器                            | 159 |

| 11.3.2 计数模式                              | 160 |

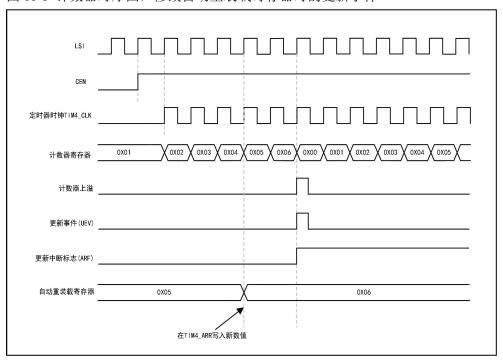

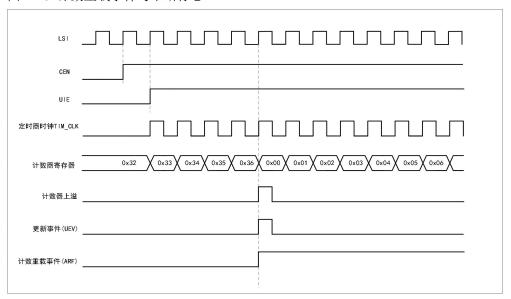

| 11.3.2.1 向上计数模式                          | 160 |

| 11.3.3 时钟源                               | 161 |

| 11.3.4 更新中断                              | 162 |

| 11.4 TIM4 寄存器描述                          | 163 |

| 11.4.1 TIM4 状态寄存器(TIM4_SR)               | 163 |

| 11.4.2 TIM4 控制寄存器 1(TIM4_CR1)            | 164 |

| 11.4.3 TIM4 预分频寄存器(TIM4_PSC)             | 165 |

| 11.4.4 TIM4 计数器寄存器(TIM4_CNT)             | 165 |

| 11.4.5 TIM4 控制寄存器 2(TIM4_CR2)            | 166 |

| 11.4.6 TIM4 自动重装载寄存器(TIM4_ARR)           | 167 |

| 11.4.7 寄存器列表                             | 168 |

| 12 独立看门狗(IWDG)                           | 169 |

| 12.1 综述                                  | 169 |

| 12.2 特性                                  | 169 |

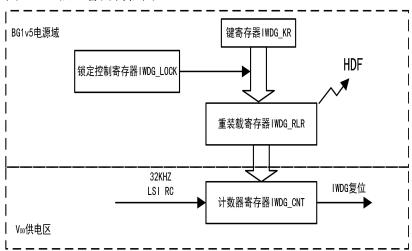

| 12.3 IWDG 功能描述                           | 170 |

| 12.3.1 时基单元                              | 170 |

| 12.3.1.1 计时时间                            | 170 |

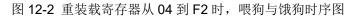

| 12.3.2 喂狗与饿狗                             | 171 |

| 12.3.3 看门狗寄存器保护机制                        | 171 |

| 12.3.3.1 生效保护机制                          | 171 |

| 12.3.3.2 失效保护机制                          | 171 |

| 12.3.4 独立看门狗中断                           | 172 |

| 12.3.5 调试模式                              | 172 |

| 12.4 寄存器描述                               | 173 |

| 12.4.1 IWDG 重装载寄存器(IWDG_RLR)             | 173 |

| 12.4.2 IWDG 计数器寄存器(IWDG_CNT)             | 173 |

| 12.4.3 IWDG 控制寄存器(IWDG_CR)               | 173 |

| 12.4.4 IWDG 键寄存器(IWDG KR)                | 175 |

| 12.4.5 IWDG 状态寄存器(IWDG_SR)       | 175 |

|----------------------------------|-----|

| 12.4.6 IWDG 保护机制控制寄存器(IWDG_LOCK) | 175 |

| 12.4.7 寄存器列表                     | 177 |

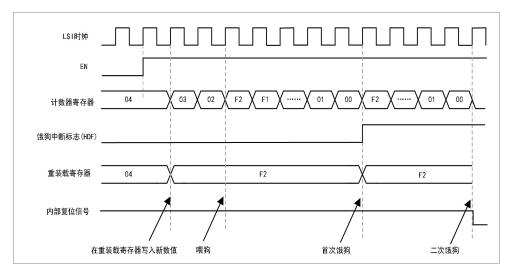

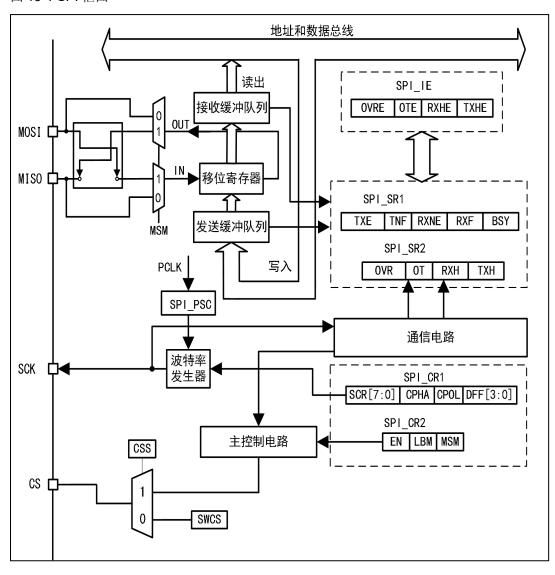

| 13 串行外设接口(SPI)                   | 178 |

| 13.1 综述                          | 178 |

| 13.2 特性                          | 178 |

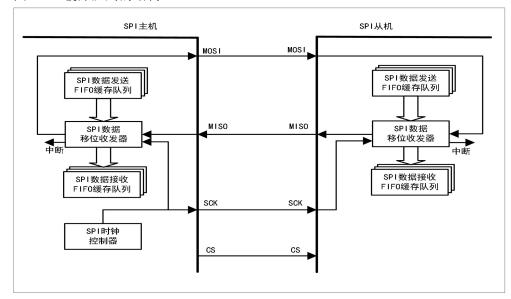

| 13.3 功能描述                        | 179 |

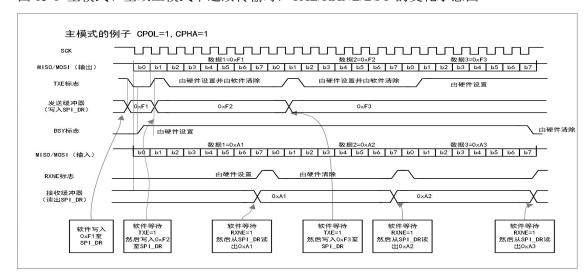

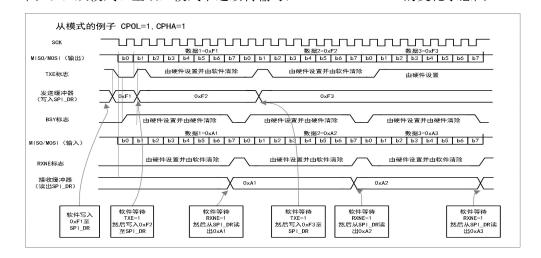

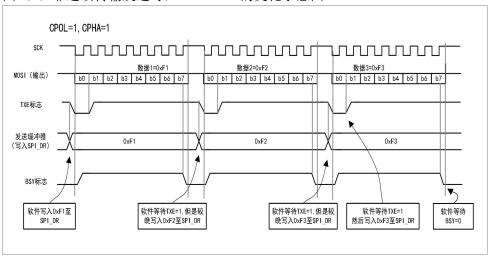

| 13.3.1 SPI 通讯                    | 181 |

| 13.3.1.1 SPI 波特率                 | 181 |

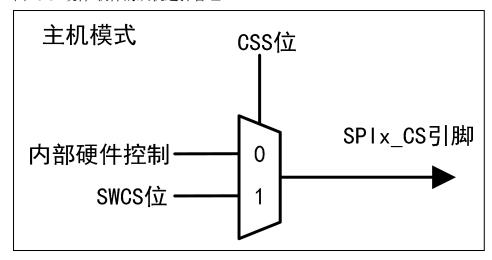

| 13.3.1.2 从机选择信号(CS)控制            | 181 |

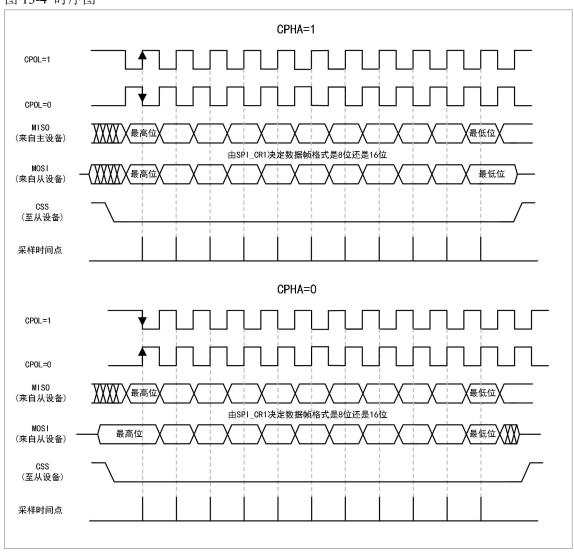

| 13.3.1.3 时钟信号的相位和极性              | 182 |

| 13.3.1.4 数据帧格式                   | 183 |

| 13.3.1.5 缓冲队列(FIFO)              | 183 |

| 13.3.2 状态标志                      | 184 |

| 13.3.2.1 发送缓冲器空闲(TXE)            | 184 |

| 13.3.2.2 接收缓冲器非空(RXNE)           | 184 |

| 13.3.2.3 忙(BSY)                  | 184 |

| 13.3.3 错误标志                      | 185 |

| 13.3.3.1 溢出错误                    | 185 |

| 13.3.3.2 超时错误                    | 185 |

| 13.3.4 配置 SPI 为主机模式              | 186 |

| 13.3.4.1 配置步骤                    | 186 |

| 13.3.4.2 数据发送过程                  | 186 |

| 13.3.4.3 数据接收过程                  | 186 |

| 13.3.5 配置 SPI 为从机模式              | 187 |

| 13.3.5.1 配置步骤                    | 187 |

| 13.3.5.2 数据发送过程                  | 187 |

| 13.3.5.3 数据接收过程                  | 187 |

| 13.3.6 连续和非连续传输                  | 188 |

| 13.3.7 关闭 SPI                    | 188 |

| 13.3.8 SPI 中断                    | 189 |

| 13.3.8.1 接收 FIFO 溢出              | 189 |

| 13.3.8.2 接收 FIFO 超时              | 189 |

| 13.3.8.3 接收 FIFO 半满              | 189 |

| 13.3.8.4 发送 FIFO 过半              | 189 |

| 13.4 寄存器描述                       | 190 |

| 13.4.1 SPI 控制寄存器 1 (SPI_CR1)     | 190 |

| 13.4.2 SPI 控制寄存器 2( SPI_CR2)     | 191 |

| 13.4.3 SPI 数据寄存器(SPI_DR)         | 192 |

| 13.4.4 SPI 状态寄存器(SPI_SR1)        | 193 |

| 13.4.5 SPI 波特率预分频寄存器(SPI_BR)     | 194 |

| 13.4.6 SPI 中断使能寄存器(SPI_IE)       | 195 |

| 13.4.7 SPI 状态寄存器 2(SPI_SR2)      | 196 |

| 13 4 8 SPI 中断标志清除寄存器(SPI JFC)    | 197 |

| 13.4.9 SPI 片选信号控制寄存器(SPI_CSS) | 198       |

|-------------------------------|-----------|

| 13.4.10 寄存器列表                 | 199       |

| 14 I2C 接口                     | 200       |

| 14.1 综述                       | 200       |

| 14.2 特性                       | 200       |

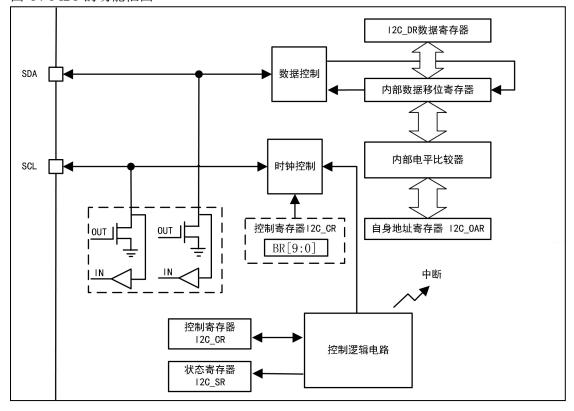

| 14.3 I2C 功能描述                 | 201       |

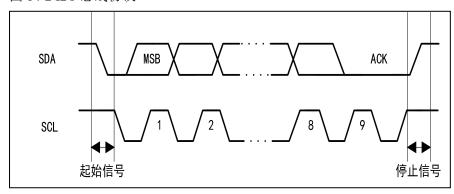

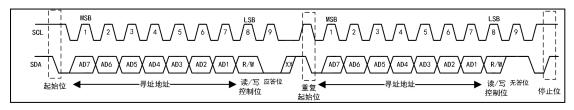

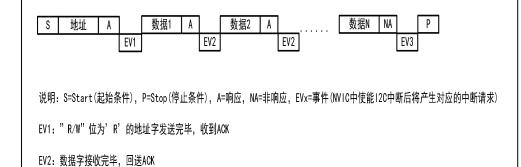

| 14.3.1 I2C 通信                 | 202       |

| 14.3.1.1 I2C 波特率              | 202       |

| 14.3.1.2 空闲状态                 | 203       |

| 14.3.1.3 起始信号(Start)          | 203       |

| 14.3.1.4 应答信号(ACK)            | 203       |

| 14.3.1.5 地址字(ADDR)与方向         | 203       |

| 14.3.1.6 数据字(DATA)            | 204       |

| 14.3.1.7 停止信号(Stop)           | 204       |

| 14.3.1.8 重复起始信号               | 204       |

| 14.3.1.9 广播                   | 204       |

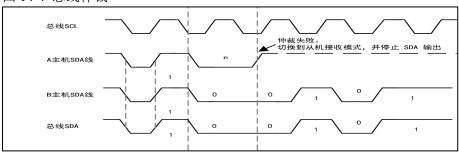

| 14.3.1.10 总线仲裁(SDA 仲裁)        | 205       |

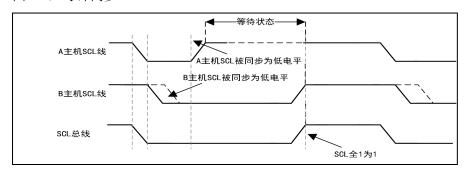

| 14.3.1.11 时钟同步(SCL 同步)        | 205       |

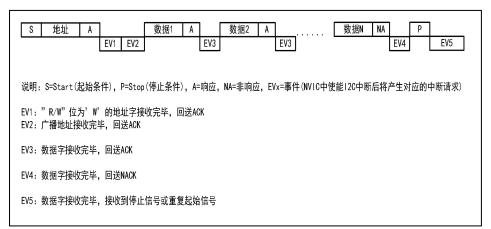

| 14.3.2 从机模式                   | 206       |

| 14.3.2.1 从发送器                 | 206       |

| 14.3.2.2 从接收器                 | 207       |

| 14.3.2.3 通信终止                 | 207       |

| 14.3.3 主机模式                   | 208       |

| 14.3.3.1 主发送器                 | 208       |

| 14.3.3.2 主接收器                 | 209       |

| 14.3.3.3 通信终止                 | 209       |

| 14.3.4 状态信息和中断请求              | 210       |

| 14.3.5 I2C 时序约束               | 错误!未定义书签。 |

| 14.3.5.1 上升时间                 | 错误!未定义书签。 |

| 14.3.5.2 上拉电阻                 | 错误!未定义书签。 |

| 14.3.5.3 高电平检测时间控制            | 错误!未定义书签。 |

| 14.4 寄存器描述                    | 211       |

| 14.4.1 I2C 控制寄存器 I2C_CR       | 211       |

| 14.4.2 I2C 状态寄存器 I2C_SR       | 213       |

| 14.4.3 I2C 数据寄存器 I2C_DR       | 213       |

| 14.4.4 I2C 地址寄存器 I2C_OAR      | 213       |

| 14.4.5 I2C 控制清除寄存器 I2C_CCR    | 215       |

| 14.4.6 寄存器列表                  | 216       |

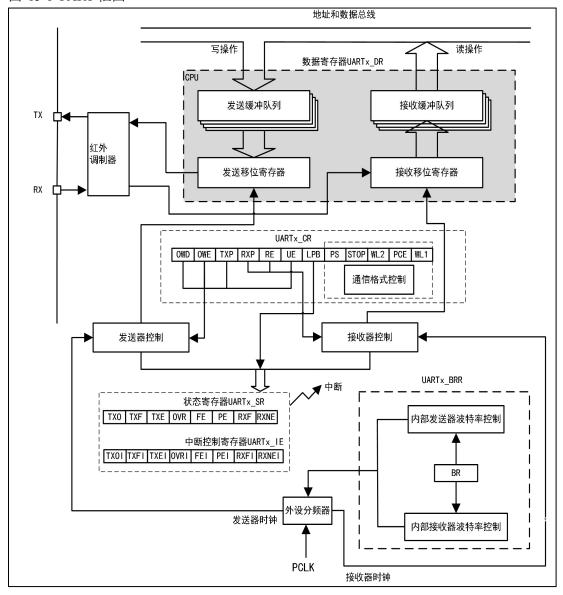

| 15 通用异步收发器(UART)              | 217       |

| 15.1 综述                       | 217       |

| 15.2 特性                       | 217       |

| 15.3 UART 功能描述                | 218       |

| 15.3.1 UART 通讯                | 219       |

| 15 3 1 1 IJART 波特率            | 220       |

| 15.3.1.2 标准波特率误差                      | 220 |

|---------------------------------------|-----|

| 15.3.1.3 空闲状态                         | 220 |

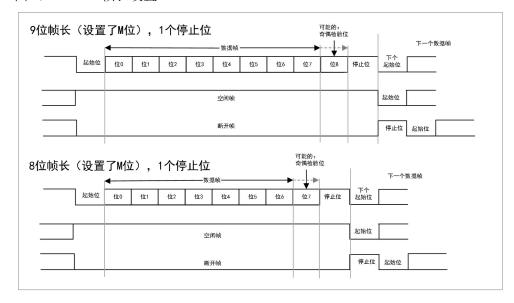

| 15.3.1.4 起始位(Start)                   | 221 |

| 15.3.1.5 数据帧(DATA)                    | 221 |

| 15.3.1.6 校验位                          | 221 |

| 15.3.1.7 停止位(Stop)                    | 221 |

| 15.3.1.8 缓冲队列(FIFO)                   | 222 |

| 15.3.2 启用 UART 功能                     | 223 |

| 15.3.2.1 配置步骤                         | 223 |

| 15.3.2.2 发送器                          | 223 |

| 15.3.2.3 接收器                          | 223 |

| 15.3.3 状态和中断                          | 224 |

| 15.3.3.1 接收 FIFO 非空(RXNE)             | 224 |

| 15.3.3.2 接收 FIFO 全满(RXF)              | 224 |

| 15.3.3.3 发送 FIFO 为空(TXE)              | 224 |

| 15.3.3.4 发送 FIFO 全满(TXF)              | 224 |

| 15.3.3.5 发送数据完毕(TXO)                  | 224 |

| 15.3.4 错误标志与中断                        | 225 |

| 15.3.4.1 校验错误(PE)                     | 225 |

| 15.3.4.2 帧错误(FE)                      | 225 |

| 15.3.4.3 溢出错误(OVR)                    | 225 |

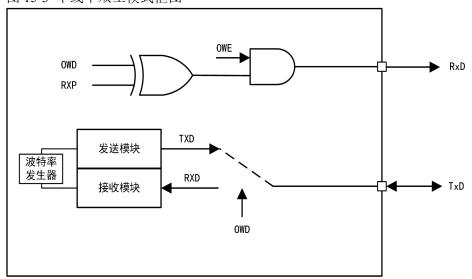

| 15.3.5 单线半双工通信                        | 226 |

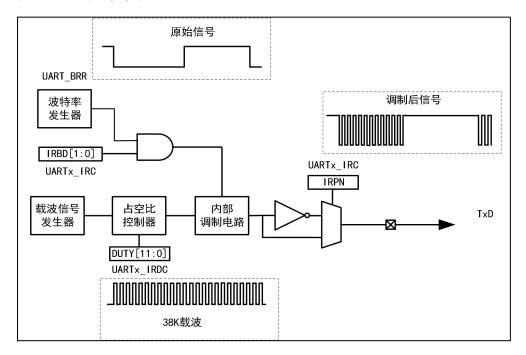

| 15.3.6 红外通信功能                         | 227 |

| 15.3.6.1 红外调制信号的占空比                   | 227 |

| 15.4 UART 寄存器描述                       | 228 |

| 15.4.1 UART 数据寄存器(UARTx_DR)           | 228 |

| 15.4.2 UART 控制寄存器(UARTx_CR)           | 229 |

| 15.4.3 UART 波特率寄存器(UARTx_BRR)         | 231 |

| 15.4.4 UART 中断控制寄存器(UARTx_IE)         | 232 |

| 15.4.5 UART 状态寄存器(UARTx_SR)           | 234 |

| 15.4.6 UART 发送 FIFO 复位寄存器(UARTx_TXFR) | 236 |

| 15.4.7 UART 接收 FIFO 复位寄存器(UARTx_RXFR) | 236 |

| 15.4.8 UART 红外调制控制寄存器(UARTx_IRC)      | 237 |

| 15.4.9 UART 红外调制占空比控制寄存器(UARTx_IRDC)  | 238 |

| 15.4.10 寄存器列表                         | 239 |

| 16 片内闪存控制器(IFMC)                      | 240 |

| 16.1 综述                               | 240 |

| 16.2 特性                               | 240 |

| 16.3 IFMC 功能描述                        | 241 |

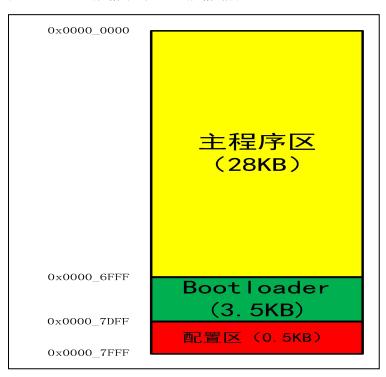

| 16.3.1 闪存模块组织                         | 241 |

| 16.3.1.1 20K 字节规格                     | 241 |

| 16.3.1.2 32K 字节规格                     | 241 |

| 16.3.2 读操作                            | 243 |

| 16.3.2.1 访问时间调节器                      | 243 |

| 16.3.3 IFMC 安全机制                 | 243 |

|----------------------------------|-----|

| 16.3.3.1 IFMC 解锁安全机制             | 243 |

| 16.3.4 IFMC 写入和擦除操作              | 244 |

| 16.3.4.1 写入和擦除时钟配置               | 244 |

| 16.3.4.2 写操作                     | 244 |

| 16.3.4.3 页擦除                     | 245 |

| 16.3.4.4 全片擦除                    | 245 |

| 16.3.5 配置区操作                     | 246 |

| 16.3.6 用户定义 ID(UDID)             | 247 |

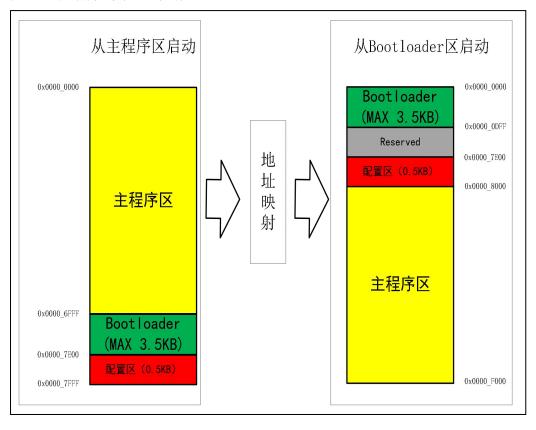

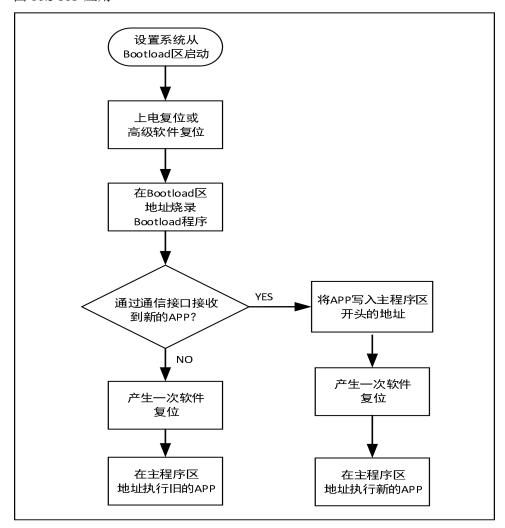

| 16.3.7 系统启动配置                    | 247 |

| 16.3.8 Flash 读保护                 | 248 |

| 16.3.9 状态和中断                     | 249 |

| 16.3.9.1 IFMC 写操作命令完成(WOV)       | 249 |

| 16.3.9.2 IFMC 页擦除操作命令完成(POV)     | 249 |

| 16.3.9.3 IFMC 全片擦除操作命令完成(COV)    | 249 |

| 16.3.9.4 IFMC 操作忙(BUSY)          | 249 |

| 16.3.9.5 IFMC 操作错误(CERR)         | 249 |

| 16.3.9.6 IFMC 密码错误(KERR)         | 249 |

| 16.3.9.7 IFMC 地址错误(AERR)         | 250 |

| 16.4 IFMC 寄存器描述                  | 251 |

| 16.4.1 IFMC 控制寄存器(IFMC_CR)       | 251 |

| 16.4.2 IFMC 状态寄存器(IFMC_SR)       | 252 |

| 16.4.3 IFMC 中断控制寄存器(IFMC_IE)     | 253 |

| 16.4.4 IFMC 地址寄存器(IFMC_AR)       | 254 |

| 16.4.5 IFMC 数据寄存器(IFMC_DR)       | 254 |

| 16.4.6 IFMC 预分频寄存器(IFMC_PSC)     | 255 |

| 16.4.7 IFMC BOOT 状态寄存器(IFMC_BSR) | 255 |

| 16.4.8 IFMC 读保护状态寄存器(IFMC_RPT)   | 256 |

| 16.5 寄存器列表                       | 257 |

| 17 器件电子签名(ID)                    | 258 |

| 17.1 综述                          | 258 |

| 17.2 特性                          | 258 |

| 17.3 用户定义 ID 寄存器(ID_UDID)        | 259 |

| 17.4 产品唯一身份标识 ID 寄存器 1(ID_UID1)  | 260 |

| 17.5 产品唯一身份标识 ID 寄存器 2(ID_UID2)  | 260 |

| 17.6 产品唯一身份标识 ID 寄存器 3(ID_UID3)  | 261 |

| 17.7 芯片配置 ID 寄存器(ID_CID)         | 262 |

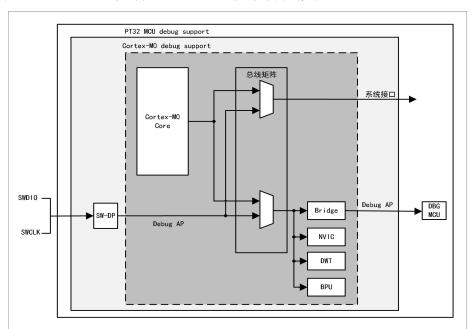

| 18 调试支持(DBG)                     | 263 |

| 18.1 综述                          | 263 |

| 18.2 ARM 参考文献                    | 264 |

| 18.3 引脚分布和 SW 端口引脚               | 264 |

| 18.3.1 灵活的 SW 端口引脚分配             | 264 |

| 18.3.2 内部上拉和下拉                   | 264 |

| 18.4 SW 调试端口                     | 265 |

| 265 | 18.4.1 SW 协议介绍                             |

|-----|--------------------------------------------|

| 265 | 18.4.2 SW 协议序列                             |

| 266 | 18.4.3 SW-DP 状态机                           |

| 266 | 18.4.4 DP 和 AP 读/写访问                       |

| 267 | 18.4.5 SW-DP 寄存器                           |

| 268 | 18.4.6 SW-AP 寄存器                           |

| 269 | 18.5 内核调试                                  |

| 270 | 18.6 BPU (Break Point Unit)                |

| 270 | 18.6.1 BPU 功能                              |

| 270 | 18.7 DWT (数据观察点触发 data watchpoint trigger) |

| 270 | 18.7.1 DWT 功能                              |

| 270 | 18.7.2 DWT 程序计数器采样寄存器                      |

| 270 | 18.8 MCU 调试模块                              |

# 文中的缩写

## 寄存器描述表中使用的缩写列表

在对寄存器的描述中使用了下列缩写:

| RW  | read / write,软件能读写此位。                        |

|-----|----------------------------------------------|

| R   | read-only,软件只能读此位。                           |

| W   | write-only, 软件只能写此位,读此位将返回复位值。               |

| Rw1 | read/clear,软件可以读此位,也可以通过写'1'清除此位,写'0'对此位无影响。 |

| Rw0 | read/clear,软件可以读此位,也可以通过写'0'清除此位,写'1'对此位无影响。 |

| Res | Reserved,保留位,必须保持默认值不变                       |

| В   | Byte                                         |

| b   | bit                                          |

| UD  | 复位值 、User Define(用户定义)                       |

| MD  | 复位值 、Manufacturers Define(制造商定义)             |

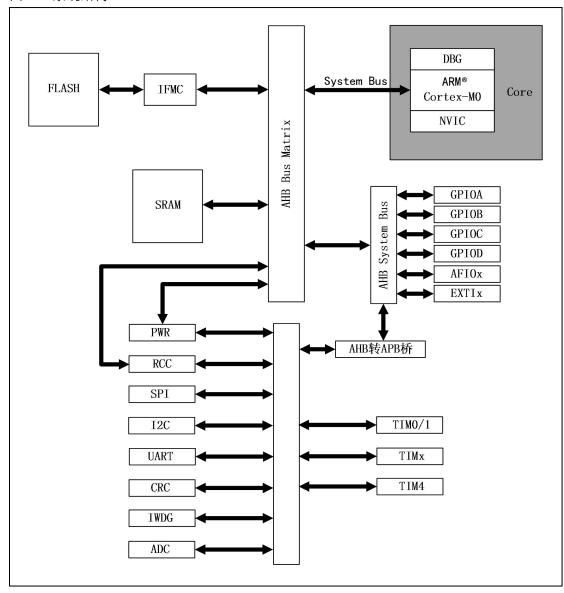

## 1 存储器和总线构架

## 1.1 系统构架

- 一个驱动单元

- Cortex™-M0 内核系统总线(S-bus)

- 四个被动单元

- 内部 SRAM

- 内部 Flash 闪存存储器

- AHB 所连接的所有外设

- AHB 到 APB 的桥,它连接的所有 APB 设备

图 1-1 系统结构

#### 1.1.1 系统总线

此总线连接 Cortex™-M0 内核的系统总线(外设总线)到总线矩阵,总线矩阵协调内核与外部总线的访问。

### 1.1.2 AHB/APB 桥(APB)

"AHB/APB 桥"在 AHB 和 APB 总线间提供同步连接。AHB 和 APB 的操作速度均与系统时钟 SYS CLK 同步。

连接到每个桥的不同外设的地址映射请参考表 1-1。在每一次复位过程当中,除 SRAM 以外的 所有外设都被关闭。

注意:对 AHB 或 APB 总线上的寄存器进行 8 位或者 16 位操作时,由于数据字节以小端格式存放在存储器中,故有:

- 1. 读操作: 该操作会被自动转换成32位的读,对应的数据将按照小端格式被存储在中间变量;

- 2. 写操作: 总线和桥会自动将8位或者16位的写入数据扩展,并将缺失的高位补0,以配合32位的向量。

## 1.2 存储器组织

程序存储器、数据存储器、寄存器和输入输出端口被组织在同一个 4GB 的线性地址空间内。

数据字节以小端格式存放在存储器中。一个字里的最低地址字节被认为是该字的最低有效字节,而最高地址字节是最高有效字节。

外设寄存器的映像请参考相关外设章节,下面列出芯片的具体地址分配。

表 1-1 AHB 地址分配

| 地址范围                      | 大小        | 外设                           |

|---------------------------|-----------|------------------------------|

| 0x0000_0000 - 0x0000_7FFF | 32KB      | 指令 FLASH 空间                  |

| 0x0000_8000 - 0x0000_F7FF | 30KB(Max) | FLASH 主代码空间映射 <sup>(1)</sup> |

| 0x0000_F800 - 0x1FFF_FFFF |           | 保留                           |

| 0x2000_0000 - 0x2000_07FF | 2KB       | SRAM 数据区                     |

| 0x2000_0800 - 0x3FFF_FFFF |           | 保留                           |

| 0x4000_0000 - 0x4001_7FFF | 96KB      | APB                          |

| 0x4001_8000 - 0x4001_EFFF |           | 保留                           |

| 0x4001_F000 - 0x4001_FFFF | 4KB       | 系统控制寄存器区                     |

| 0x4002_0000 - 0x47FF_FFFF |           | 保留                           |

| 0x4800_0000 - 0x4800_0FFF | 4KB       | GPIOA 寄存器区                   |

| 0x4800_1000 - 0x4800_1FFF | 4KB       | GPIOB 寄存器区                   |

| 0x4800_2000 - 0x4800_2FFF | 4KB       | GPIOC 寄存器区                   |

| 0x4800_3000 - 0x4800_3FFF | 4KB       | GPIOD 寄存器区                   |

| 0x4800_4000 - 0xE000_DFFF |           | 保留                           |

| 0xE000_E000 - 0xE000_EFFF | 4KB       | 内核控制寄存器区                     |

| 0xE000_F000 - 0xFFFF_FFFF |           | 保留                           |

| 0xF000_0000 - 0xF000_0FFF | 4KB       | 保留                           |

| 0xF000_1000 - 0xFFFF_FFFF |           | 保留                           |

(1):仅在执行 bootloader 时有效,大小与 bootloader 大小相关,更多信息请参考"16 片内闪存控制器(IFMC)"

注意:访问非法的保留地址将导致MCU彻底失效,并且无法恢复。

表 1-2 APB 地址分配

| 地址范围                      | 大小   | 外设      |

|---------------------------|------|---------|

| 0x4000_0000 - 0x4000_07FF | 2KB  | IFMC    |

| 0x4000_0800 - 0x4000_0FFF | 2KB  | 保留      |

| 0x4000_1000 - 0x4000_13FF | 1KB  | TIM2    |

| 0x4000_1400 - 0x4000_17FF | 1KB  | TIM3    |

| 0x4000_1800 - 0x4000_1BFF | 1KB  | 外设占用(1) |

| 0x4000 1C00 – 0x4000 1FFF | 1KB  | TIM4    |

| 0x4000_2000 - 0x4000_2FFF | 4KB  | 保留      |

| 0x4000_3000 - 0x4000_37FF | 2KB  | IWDG    |

| 0x4000_3800 - 0x4000_3BFF | 1KB  | 保留      |

| 0x4000_3C00 - 0x4000_3FFF | 1KB  | CRC     |

| 0x4000_4000 - 0x4000_43FF | 1KB  | 保留      |

| 0x4000_4400 - 0x4000_47FF | 1KB  | UART0   |

| 0x4000_4800 - 0x4000_53FF | 3KB  | 保留      |

| 0x4000_5400 - 0x4000_57FF | 1KB  | I2C     |

| 0x4000_5800 - 0x4000_5BFF | 1KB  | 保留      |

| 0x4000_5C00 - 0x4001_23FF | 50KB | 保留      |

| 0x4001_2400 - 0x4001_27FF | 1KB  | ADC     |

| 0x4001_2800 - 0x4001_2BFF | 1KB  | 保留      |

| 0x4001_2C00 - 0x4001_2FFF | 1KB  | TIM1    |

| 0x4001_3000 - 0x4001_33FF | 1KB  | SPI     |

| 0x4001_3400 - 0x4001_37FF | 1KB  | 保留      |

| 0x4001_3800 - 0x4001_3BFF | 1KB  | UART1   |

| 0x4001_3C00 - 0x4001_3FFF | 1KB  | 保留      |

| 0x4001_4000 - 0x4001_43FF | 1KB  | 保留      |

| 0x4001_4400 - 0x4001_7FFF | 15KB | 保留      |

<sup>(1):</sup>该地址被分配到不同的外设,详见相关寄存器说明。

#### 1.3 嵌入式 SRAM

PT32x00x 内置最大 2K 字节的 SRAM。它可以以字节、半字(16 位)或全字(32 位)访问。 SRAM 的起始地址是 0x2000 0000。

#### 1.4 嵌入式 Flash 闪存

PT32x00x 内置的闪存存储器可以用于在线编程(ICP),在线编程(In-Circuit Programming - ICP)方式用于更新闪存存储器的全部内容,它通过 SWD 协议或系统加载程序(Bootloader)下载用户应用程序到微控制器中。ICP 是一种快速有效的编程方法,消除了封装和管座的困扰。高性能的闪存模块有以下的主要特性:

最大 32K 字节的闪存存储器结构,下面罗列存储器的组成部分:

- 主程序区

- Bootloader 区

- 用户配置区

通过片内闪存控制器 IFMC 可以便捷的控制 Flash 闪存,有关 IFMC 的详细信息,请参考"16 片内闪存控制器(IFMC)"。

注意: PT32x00x 不支持中断向量表重映射, 故不支持IAP 应用。

## 1.5 启动配置

PT32x00x 支持两种启动模式:

- 从主程序区启动

- 从 Bootloader 区启动

这两种启动模式都基于 Flash 片内闪存,通过特定的程序配置以实现不同的启动模式,而无需外部硬件的介入。

注意:默认从主程序区启动,关于从Bootloader 区启动的详细信息,请参考"16.3.6 系统启动 配置"

## 2 CRC

#### 2.1 综述

CRC 算法基于模 2 除法的原理,这需要占用一定的系统计算资源。 集成的硬件 CRC 是独立于系统的,它速度更快,更加灵活,且运行时并不占用系统计算资源,在一个时钟周期内,就可以完成 CRC 的计算。

## 2.2 特性

- 16位的可编程的多项式,适用于多种不同的通信标准

- 16 位的可编程的种子(初始值),适用于多种不同的通信标准

- 即算即得,单个 PCLK 的 CRC 计算时间

- 硬件反转,以支持不同类型的数据格式

- 输入位序列反转

- 输入字节序列反转

- 输出位序列反转

- 独立的输入/输出数据寄存器

## 2.3 CRC 功能描述

CRC 即循环冗余校验,是一种数据传输检错功能,CRC 对一帧数据中的有效数据进行多项式计算,并将得到的结果附在这帧数据后面;它被广泛用于各种通信协议,常见的有 USB, Modbus 等等。

在实际通信中、通信的收发双方都约定了同一种 CRC 算法,如果数据帧在传输过程中没有被破坏,则双方通过 CRC 计算得出的结果将一致。

#### 2.3.1 多项式

多项式用于生成有效数据的 CRC 校验码,又称为"生成多项式"。

收发双方约定了同一个多项式,利用这个多项式,对发送或接收的有效数据进行模 2 除法,以求出 CRC 校验码。

- 对于发送方, 计算得出的 CRC 校验码被附在帧数据后面。

- 对于接收方, 计算得出的 CRC 校验码会与帧数据之后的 CRC 校验码进行对比, 当两者一致, 才会接收本次数据。

常用的 CRC 多项式如下表所示:

表 2-1 常用的 CRC 多项式

| 名称        | 多项式                                                 | 16 进制值  | 应用举例          |

|-----------|-----------------------------------------------------|---------|---------------|

| CRC-16    | X <sup>16</sup> +X <sup>15</sup> +X <sup>2</sup> +1 | 0X18005 | Modbus, USB   |

| CRC-CCITT | X <sup>16</sup> +X <sup>12</sup> +X <sup>5</sup> +1 | 0X11021 | HDLC, PPP-FCS |

例如上表的 CRC-16, CRC 规定了多项式中有幂次为 1, 没有幂次为 0, 首尾一定要是 1, 所以多项式 CRC-16 的二进制值为"1 1000 0000 0000 0101", 用 16 进制表示为 0X18005。

注意:由于最高位总是为1,一般会将最高位忽略,但其本质是不变的。

示例, 求有效数据"0x0180"的 CRC-16 结果:

- 0x0180 的二进制值为"1 1000 0000"

- CRC 为 16 位, 0x0180 作为被除数,后面补上 16 个'0': "1 1000 0000 0000 0000 0000 0000 0000"

- CRC-16 多项式的 16 进制值为 0x18005,作为除数,其二进制值为"1 1000 0000 0000 0101"

图 2-1 CRC-16 计算过程

1(商)

10100000000(余数)

最终的余数"101 0000 0000"就是 0x0180 的 CRC-16 结果,将其转换为 16 进制,结果为 0x500。

## 2.3.2 种子(初始值)

初始值的作用在于防止全'0'的数据 CRC 结果一直为 0, 它执行一个"异或"的操作, 对于有效数据:

- 当有效数据为'0',初始值为'1'时,最终有效数据=0⊕1=1;

- 当有效数据为'1',初始值为'1'时,最终有效数据=1⊕1=0;

合理的设置初始值有利于提高通信的鲁棒性,在一些标准的通信协议 CRC 中,对初始值也做出了相关要求。

注意:初始值的作用时机总是在反转功能作用之后。

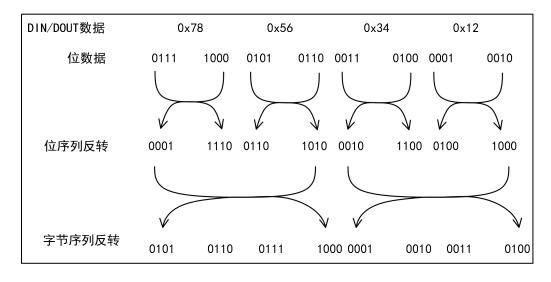

#### 2.3.3 反转功能

CRC 模块的数据格式默认为 MSB(高位在前),反转功能用于保证输入/输出数据格式间的兼容性:

- 对于输入: 当输入数据为 LSB 格式时,可以使用输入位序列反转功能,将输入数据的格式转换成 MSB 格式。

- 对于输出: 当输出数据需要为 LSB 格式时,可以使用输出位序列反转功能,将输出数据的格式转换成 LSB 格式。

- 特别地、当外部传入的数据是低字节在前,高字节在后的 16 位数据格式时,可以使用字节序列反转功能。

注意: 当同时使能了输入字节序列反转功能和输入位序列反转功能时,输入字节序列反转功能被首先生效。

图 2-2 反转功能图

## 2.4 寄存器描述

# 2.4.1 CRC 控制寄存器(CRC\_CR)

(地址: 0x4000\_3C00)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | 1   | -   | -   | -   | -   | 1   | -   | -   | 1   | -   | -   | 1   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5    | 4   | 3    | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|------|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | COSN | CBN | CISN | CIS | CRS | CEN |

| R/W | Res | RW   | RW  | RW   | RW  | Rw1 | RW  |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0   | 0    | 0   | 0   | 0   |

|          | CEN: CRC 模块使能控制(CRC enable)                     |

|----------|-------------------------------------------------|

| 位 0      | 0: CRC 模块失能                                     |

|          | 1: CRC 模块使能                                     |

|          | CRS: CRC 复位控制(CRC reset control)                |

| 位 1      | 0: 无效                                           |

|          | 1: 复位 CRC_DOUT 到默认状态                            |

|          | CIS: CIS 输入选择(CRC input select)                 |

| 位 2      | 0: 8位数据宽度                                       |

|          | 1: 16 位数据宽度                                     |

|          | CISN: 输入位序列反转(CRC input bit sequence reversal)  |

| 位3       | 无论 16 位和 8 位模式下,输入位序列反转只在字节内进行                  |

| <u> </u> | 0: 不反转                                          |

|          | 1: 反转                                           |

|          | CBN: 输入字节序列反转(CRC input byte sequence reversal) |

| 位 4      | 输入字节序列反转只对 16-bit 模式有效                          |

| <u> </u> | 0: 不反转                                          |

|          | 1: 反转                                           |

|          | COSN: 输出位序列反转(CRC output bit sequence reversal) |

| 位 5      | 输出位序列反转是对整个 16-bit 输出而言,而不是字节内部反转               |

|          | 0: 不反转                                          |

|          | 1: 反转                                           |

| 位 31: 6  | 保留。必须保持为 0。                                     |

# 2.4.2 CRC 种子寄存器(CRC\_SEED)

(地址: 0x4000\_3C04)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|----|----|----|------|--------|----|----|----|----|----|----|----|

| 位域  |    |    |    |    |    |    |    | SEED | [15:0] |    |    |    |    |    |    |    |

| R/W | RW   | RW     | RW | RW | RW | RW | RW | RW | RW |

| 复位  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1    | 1      | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 位 15: 0  | SEED[15:0]: CRC 种子(CRC seed) |

|----------|------------------------------|

| 位 31: 16 | 保留。必须保持为 0。                  |

## 2.4.3 CRC 多项式寄存器(CRC\_POLY)

(地址: 0x4000 3C08)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7      | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----|----|----|----|----|----|----|----|------|--------|----|----|----|----|----|----|----|

| 位域  |    |    |    |    |    |    |    | POLY | [15:0] |    |    |    |    |    |    |    |

| R/W | RW   | RW     | RW | RW | RW | RW | RW | RW | RW |

| 复位  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  | 0  | 1  | 0  | 1  |

|          | POLY[15:0]: CRC 多项式(CRC poly)           |

|----------|-----------------------------------------|

|          | 0x8005: 表示 G(X) = X^16 + X^15 + X^2 + 1 |

| 位 15: 0  | 0x1021: 表示 G(X) = X^16 + X^12 + X^5 + 1 |

|          | 其他: 保留                                  |

|          | 注: 最高位的因子不需要写入寄存器                       |

| 位 31: 16 | 保留。必须保持为 0。                             |

# 2.4.4 CRC 数据输入寄存器(CRC\_DIN)

(地址: 0x4000\_3C0C)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15        | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|-----------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 位域  | DIN[15:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| R/W | W         | W  | W  | W  | W  | W  | W | W | W | W | W | W | W | W | W | W |

| 复位  | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|          | DIN[15:0]: CRC 数据输入寄存器(CRC data input) |

|----------|----------------------------------------|

|          | 该寄存器只写不可读,读恒为0                         |

| 位 15: 0  | 注:                                     |

|          | 1.8 位模式下, 仅低 8 位有效                     |

|          | 2. 仿真模式下对该寄存器写入的数据无效                   |

| 位 31: 16 | 保留。必须保持为 0。                            |

# 2.4.5 CRC 数据输出寄存器(CRC\_DOUT)

(地址: 0x4000\_3C10)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | 1   | -   | -   | -   | -   | -   | -   | -   | 1   | -   | -   | 1   | 1   | -   | 1   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8    | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|----|----|----|----|----|----|---|------|--------|---|---|---|---|---|---|---|

| 位域  |    |    |    |    |    |    |   | DOUT | [15:0] |   |   |   |   |   |   |   |

| R/W | R  | R  | R  | R  | R  | R  | R | R    | R      | R | R | R | R | R | R | R |

| 复位  | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1    | 1      | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 位 15: 0  | DOUT[15:0]: CRC 数据输出寄存器(CRC data output) |

|----------|------------------------------------------|

| 业13; 0   | 该寄存器只读不可写                                |

| 位 31: 16 | 保留。必须保持为0。                               |

# 2.4.6 寄存器列表

| 地址          | 寄存器      | 描述         | 备注          |

|-------------|----------|------------|-------------|

| 0x4000_3C00 | CRC_CR   | CRC 控制寄存器  | CRC_CR 说明   |

| 0x4000_3C04 | CRC_SEED | CRC 种子寄存器  | CRC_SEED 说明 |

| 0x4000_3C08 | CRC_POLY | CRC 多项式寄存器 | CRC_POLY 说明 |

| 0x4000_3C0C | CRC_DIN  | CRC 数据输入   | CRC_DIN 说明  |

| 0x4000_3C10 | CRC_DOUT | CRC 数据输出   | CRC_DOUT 说明 |

# 3 电源控制(PWR)

#### 3.1 综述

PWR 列举了芯片内部与电源相关的所有资源,包括内部的电源电压调节器、可编程的电源电压监测器、低功耗模式。

## 3.2 特性

- 集成的电源调节器,提供3路内部电源、均可通过ADC内部通道进行访问:

- ◆ BG1v5 1.5V 精度 5%

- ◆ BG1v2 1.2V 精度 5%

- ◆ BG1v0 1.0V 精度 0.5%

- 多挡位、支持复位或中断的可编程电源电压检测器

- 在低功耗模式下,提供两种低功耗模式:

- ◆ 睡眠模式

- ◆ 深度睡眠模式

- 深度睡眠下、典型功耗仅为 0.8uA

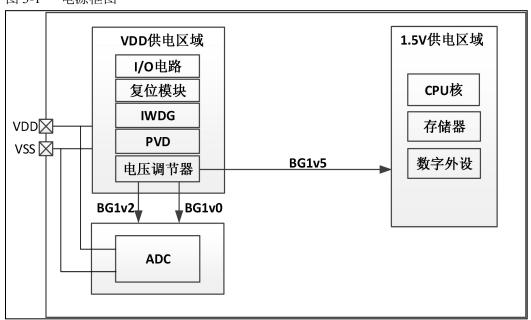

#### 3.3 电源调节器

PT32x00x 支持在超宽电压范围内工作、工作电压(VDD)详见《PT32x00x 数据手册》。

通过内置的电源调节器提供内部所需的 1.5V 电源 BG1v5、1.2V 参考电源 BG1v2 以及 1.0V 参考电源 BG1v0。

所有的内部电源均可通过 ADC 内部通道进行访问、详见 ADC(控制寄存器 ADC\_CR)的"CHS" 位描述。

图 3-1 电源框图

### 3.3.1 电源调节器

复位后电源调节器总是使能的。根据系统运行状态、它以2种不同的模式工作。

1.运行模式:调节器以正常功耗模式提供 BG1v5、BG1v2、BG1v0 三路电源;BG1v5 作为核心电源共给内部 CPU、存储器和数字外设,并且与 BG1v2、BG1v0 一起接入 ADC 的内部模拟通道中,如图 3-1 所示。

2.低功耗模式:提供睡眠和深度睡眠两种低功耗模式,电源调节器将递进的关闭片内电源、时钟、外设,以使系统功耗大大降低。

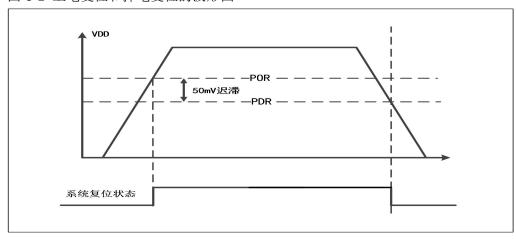

#### 3.3.2 电源复位条件

PT32x00x 内部有一个完整的上电复位(POR)和掉电复位(PDR)电路,当 VDD 电压达到工作电压时系统就能正常工作。

当 VDD 低于指定的限位电压 V<sub>POR</sub>/V<sub>PDR</sub>时,系统保持为复位状态。关于上电复位和掉电复位的 更多细节请参考"4.3 复位功能描述"和《PT32x00x 数据手册》的电气特性部分。

图 3-2 上电复位和掉电复位的波形图

### 3.3.3 可编程的电源电压监测器(PVD)

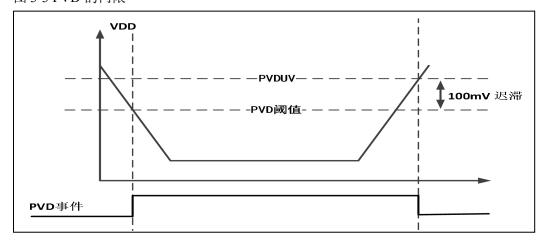

用户可以利用 PVD 对 VDD 电压进行监测, (电源电压监测器配置寄存器 PWR\_PVDR)中的"PLS"位用于设定 PVD 监控 VDD 电压的阈值。

通过将(PWR PVDR 寄存器)中的 PVDE 位置'1'以使能 PVD。

PVD 事件支持用户通过复位和中断两种形式进行访问,复位功能参考"4.3.3.1 电源低电压复位"的描述,其对应的中断事件在内部被连接到 NVIC 的第 20 号中断,如果该中断在系统中断使能寄存器 ISER 中被使能,一旦发生该事件、NVIC 就会响应 PVD 的中断请求。

PVD 事件的触发/解除机制由硬件自动控制,当 VDD 下降到"PLS 位"所设定的阈值时,PVD 中断被触发,当 VDD 上升到 PVDUV 时,PVD 中断被解除。

这一特性可用于用于执行紧急关闭任务。

#### 图 3-3 PVD 的门限

#### 3.4 低功耗模式

系统或电源复位以后,系统处于运行模式。当系统无需继续运行时,可以利用多种低功耗模式 来节省功耗;

例如等待某个外部事件时,用户可以根据最低电源消耗、唤醒时间和可用的唤醒源等条件,选定一个最佳的低功耗模式。

PT32x00x 提供了两种低功耗模式:

- 睡眠状态(Cortex™-M0 内核停止,但包括 Cortex-M0 核心的外设在内的所有外设,如 NVIC、SysTick 等仍在运行, IFMC 无法访问)

- 深度睡眠状态(除 LSI 外的所有时钟均已停止工作, 相关的片内电源以及外设被强制关闭)。

此外,在运行模式下,还可以通过以下方式降低功耗:

- 失能未被使用的时钟源

- 失能未被使用但已被使能的外设。

- 将不使用的 GPIO 做内部下拉处理

注意: BGIv5 电源的初始化依赖于LSI, 上电时, LSI 不应立刻被关闭, 否则将导致 BGIv5 异常, 详见《PT32x00x 数据手册》说明。

|       | 11-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1 | 116 |

|-------|--------------------------------------|-----|

| 表 3-1 | 低功耗模式资源-                             | 一烷  |

| 低功耗状态  | 强制关闭的时钟                                   | 强制关闭的片内电源 | 强制关闭的外设            |

|--------|-------------------------------------------|-----------|--------------------|

| 睡眠状态   | CPU 核心时钟                                  | 无         | IFMC               |

| 深度睡眠状态 | HSI 时钟<br>PLL 时钟<br>SYS_CLK 挂载的<br>所有外设时钟 | BG1v5     | PVD<br>IFMC<br>MCO |

#### 3.4.1 进入低功耗模式

通过将配置系统控制寄存器(SCR)中的 SLP 位置'1'以选定系统进入低功耗模式时、系统处于睡眠状态还是深度睡眠状态。

系统进入低功耗模式有两种方法:

- 执行 WFI 或 WFE 指令以进入低功耗模式

- 将系统控制寄存器(SCR)中的 SOE 位置'1',当系统从最低优先级的中断处理程序中退出时,立即进入低功耗模式

注意: 进入低功耗模式前,应该将所有未使用到的管脚配置为下拉输入,并清除所有管脚的复用功能可使系统功耗得到最大优化。

#### 3.4.2 睡眠状态

表 3-1 罗列了系统处于睡眠状态时、片内资源的工作状态。

如需优化功耗、在进入睡眠状态前,用户可手动关闭无需在低功耗模式下工作的外设以降低功耗。

#### 3.4.3 深度睡眠状态

表 3-1 罗列了系统处于深度睡眠状态时、片内资源的工作状态。

在深度睡眠状态下,只有 LSI 时钟挂载的外设可以正常运行,内核的寄存器、内存的信息仍保存,程序在唤醒后仍从上一次停止处执行;

除表 3-1 所罗列的在深度睡眠状态下被强制关闭外设外,其他外设均不会被强制关闭,在运行模式下使能的外设、在进入深度睡眠前应该手动关闭以避免额外功耗;

如需进一步的优化功耗,可将 LSI 时钟关闭,但 LSI 时钟挂载外设将无法工作,此时、低功耗模式的唤醒仅支持外部中断唤醒。

注意: GPIO 外部中断唤醒深度睡眠时,仅支持双沿中断、高电平中断和低电平中断。

#### 3.4.4 唤醒方式

当系统处于低功耗模式时,如果是睡眠状态,根据进入低功耗模式的指令,有相应的唤醒方式:

- WFI 指令:任意一个被 NVIC 响应的外设中断都能将系统从睡眠模式唤醒。

- WFE 指令:包括所有中断在内、所有内核支持的事件

特别地、当(系统控制寄存器 SCR)的"SWC"位为'1'时: 所有中断或事件均可唤醒。

注意:使用WFE 唤醒睡眠状态,需要在(中断挂起清除寄存器 ICPR)中清除相应的挂起标志。

如果是深度睡眠状态,根据进入低功耗模式的方法,有相应的唤醒方式:

- WFI 指令: LSI 时钟挂载外设的中断或者外部中断

- WFE 指令: LSI 时钟挂载外设的中断、外部中断、复位事件或调试模式请求事件特别地、当(系统控制寄存器 SCR)的"SWC"位为'1'时: LSI 时钟挂载外设的中断、外部中断、复位事件或者调试模式请求事件均可唤醒。

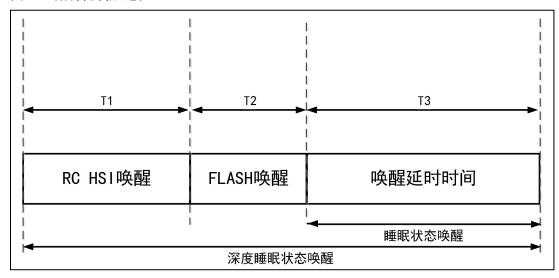

#### 3.4.5 唤醒时间

唤醒时间定义为:从唤醒事件开始至用户程序取读第一条指令。 系统从低功耗模式被唤醒时、时钟被最先唤醒,随后按照顺序唤醒 FLASH,进行唤醒延时,

最后系统重新进入运行模式。

#### 图 3-4 低功耗唤醒过程

芯片在进入低功耗模式之前,可以配置时钟配置寄存器(RCC\_CFGR)的"WKSK"位以选择系统时钟在低功耗唤醒后是否自动恢复到上一次的状态。

唤醒时间也是可配置的,通过配置时钟配置寄存器(RCC\_CFGR)的"WKDL"位改变唤醒时间,如下表(Tsys\_CLk表示单位系统时钟周期):

表 3-2 低功耗唤醒过程

| WKDL[1:0] | T1                  | T2                 | Т3                          |

|-----------|---------------------|--------------------|-----------------------------|

| 00        |                     |                    | 320 (T <sub>SYS_CLK</sub> ) |

| 01        | 16 (0(1))           | 2 (2)              | 160 (Tsys_clk)              |

| 10        | 16uS <sup>(1)</sup> | 2uS <sup>(2)</sup> | 132 (T <sub>SYS_CLK</sub> ) |

| 11        |                     |                    | 96 (T <sub>SYS_CLK</sub> )  |

#### 注:

- 1. RC HSI 唤醒时间取 VDD3.3V 时的典型值,详请参考《PT32x00x 数据手册》

- 2. FLASH 唤醒时间取 VDD3.3V 时的典型值,详请参考《PT32x00x 数据手册》

## 3.5 寄存器描述

# 3.5.1 电源电压监测器配置寄存器 PWR\_PVDR

(地址: 0x4000 1800)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3        | 2  | 1  | 0    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----------|----|----|------|

| 位域  | -   | -   | 1   | ı   | -   | 1   | -   | -   | 1   | -   | -   | ı   | PLS[2:0] |    |    | PVDE |

| R/W | Res | RW       | RW | RW | RW   |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0        | 0  | 1  | 1    |

|         | PVDE: 电源电压监测器使能(power voltage detect enable)          |

|---------|-------------------------------------------------------|

| 位 0     | O: 失能 PVD                                             |

|         | 1: 使能 PVD                                             |

|         | PLS[2:0]: PVD 电平选择(power voltage detect level select) |

|         | 这些位用于选择电源电压检测器的电压阈值                                   |

|         | 000: 4.0V                                             |

| 位 3: 1  | 001: 1.7V                                             |

|         | 010: 2.2V                                             |

|         | 011: 2.75V                                            |

|         | 100: 3.5V                                             |

|         | 注: 当 LVD 阈值设为 2.2V 或 1.7V 时,LVD 将只能够复位,而不能够中断。        |

| 位 31: 4 | 保留,必须保持为0。                                            |

# 3.5.2 系统控制寄存器(SCR)

(地址: 0x E000 ED10)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | 1   | 1   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | 1   | ı   | -   | -   | -   | 1   | ı   | 1   | 1   | -   | -   | SWC | -   | SLP | SOE | ı   |

| R/W | Res | RW  | Res | RW  | RW  | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位 0     | 保留。必须保持为0。                              |  |  |  |  |  |  |  |  |

|---------|-----------------------------------------|--|--|--|--|--|--|--|--|

|         | SOE: 低功耗模式控制                            |  |  |  |  |  |  |  |  |

| 位 1     | 0: 最低优先级的中断处理完毕后,仍处于运行模式                |  |  |  |  |  |  |  |  |

|         | 1: 最低优先级的中断处理完毕后,根据 SLP 位,立即进入睡眠或深度睡眠模式 |  |  |  |  |  |  |  |  |

|         | SLP: 低功耗模式选择                            |  |  |  |  |  |  |  |  |

| 位 2     | 0: 睡眠状态                                 |  |  |  |  |  |  |  |  |

|         | 1: 深度睡眠状态                               |  |  |  |  |  |  |  |  |

| 位 3     | 保留。必须保持为 0。                             |  |  |  |  |  |  |  |  |

|         | SWC: 低功耗唤醒控制                            |  |  |  |  |  |  |  |  |

| 位 4     | 0: 仅使能的中断或者事件可以唤醒低功耗模式                  |  |  |  |  |  |  |  |  |

|         | 1: 所有中断或者事件都可以唤醒低功耗模式                   |  |  |  |  |  |  |  |  |

| 位 31: 0 | 保留。必须保持为 0。                             |  |  |  |  |  |  |  |  |

# 3.5.3 寄存器列表

| 地址           | 寄存器      | 描述           | 备注          |

|--------------|----------|--------------|-------------|

| 0x4000_1800  | PWR_PVDR | 电源电压监测器配置寄存器 | PWR_PVDR 说明 |

| 0x E000_ED10 | SCR      | 系统控制寄存器      | SCR 说明      |

# 4 复位和时钟控制(RCC)

#### 4.1 综述

PT32x00x 内部集成了一个多功能的复位和时钟控制器;

在复位功能上、该控制器支持3种复位:系统复位、电源复位、功能复位;除高级软件复位外,所有复位均支持复位后取读复位标志。

在时钟功能上、三种不同的时钟源可被用来驱动系统时钟(SYS CLK):

- HSI 振荡器时钟

- LSI 振荡器时钟

- PLL 时钟

当不被使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗。

### 4.2 特性

- 多功能、配置灵活的复位机制

- 集成的高速 24Mhz RC 振荡器 HSI

- 集成的低功耗 32Khz RC 振荡器 LSI

- 集成的 PLL,可将 HSI 或 LSI 时钟 2 倍频作为系统时钟 SYS CLK

- 鲁棒性优异的时钟安全机制

- 配置灵活的时钟输出

#### 4.3 复位功能描述

PT32x00x 支持三种复位形式,分别为系统复位、上电复位和功能复位。

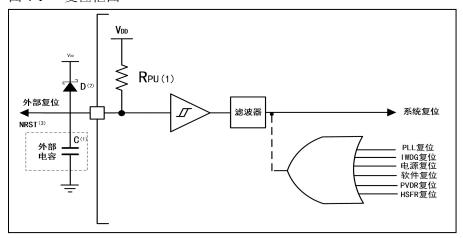

#### 图 4-1 复位框图

(1):RPU 阻值详见《PT32x00x 数据手册》

#### 注意:

- 1. 外部电容应该在1uF~10uF之间

- 2. 应当保证存在一个"IF=10mA 时,正向电压 VF 不超过 0.4V" 肖特基二极管

- 3. 即使NRST 引脚被复用,也应该保证存在外部电容。

### 4.3.1 系统复位

除了(RCC\_RSR 寄存器)中的复位状态外,系统复位将复位所有寄存器至它们的复位状态。 当发生以下任一事件时,产生一个系统复位:

- NRST 引脚上的低电平(外部复位)

- 软件复位(SF 复位)

- 独立看门狗计数终止(IWDG 复位)

- PLL 时钟失效复位 (PLL 复位)

可通过查看(RCC\_RSR 寄存器)中的复位状态以识别复位事件的来源。

#### 4.3.1.1 NRST 引脚复位

当 NRST 引脚被拉低产生外部复位时,它将产生复位脉冲到系统复位。

注意: NRST 引脚支持复用为IO,但上电时、该引脚仍默认作为NRST 引脚。

#### 4.3.1.2 软件复位

通过将 Cortex®-M0 的(中断应用和复位控制寄存器 AIRCR)中的 SYSRESETREQ 位置'1',可实现软件复位。更多信息请参考《Cortex™-M0 技术参考手册》。

#### 4.3.1.3 PLL 复位

将(RCC\_RCR 寄存器)的 PREN 位置'1'以使能 PLL 时钟失效复位,当 PLL 时钟失效时,将发生 PLL 时钟失效复位、并将(RCC\_RSR 寄存器)的 PLLR 位置'1'。

### 4.3.2 电源复位

包括(RCC\_RSR 寄存器)中的复位标志,电源复位将复位所有寄存器至它们的复位状态。 当发生以下任一事件时,产生一个电源复位:

● 芯片上电/掉电复位(POR)

#### 4.3.2.1 芯片上电/掉电复位

芯片上电/掉电复位产生条件请参考"3.3.2 电源复位条件"一节。

特别地、Flash 配置区中对配置字进行修改的操作需要产生一次 POR 复位或者高级软件复位,更多信息请参考"16.3.5 配置区操作"。

### 4.3.3 功能复位

功能复位通常具备可编程、多功能的特征;

包括(RCC\_RSR 寄存器)中的复位标志,功能复位将复位所有寄存器至它们的复位状态。 当发生以下任一事件时,产生一个功能复位:

- 电源低电压复位 (PVDR)

- 高级软件复位(HSFR)

#### 4.3.3.1 电源低电压复位

在电源 PVD 模块使能的前提下、通过将(RCC\_RCR 寄存器)中的"PDRE"位置'1'以使能该复位; 使能该复位、在电源电压低于 PVD 阈值时、将发生 PVD 复位、此时、(RCC\_RSR 寄存器)中的"PVDR"将被置'1';

通过为 PVD 模块配置相应的阈值,能够满足多档电源电压下的复位需求,更多信息请参考"3.3.3 可编程的电源电压监测器"节描述。

#### 注意:

- I. "PWR\_PVDR 寄存器"和"RCC\_RCR 寄存器"内的值在复位后即恢复到默认值 0,这意味着 PVD 的复位使能和阈值配置将在复位后失效。

- 2. 若需要 PVD 限制系统在某一电压范围才能开始工作,则必须在用户程序的最开始进行 PVD 阈值配置和 PVD 复位使能。

#### 4.3.3.2 高级软件复位

在(RCC\_RCR 寄存器)中的"HREN"位置'1'的前提下、往(RCC\_HSFRR 寄存器)中写入高级软件复位密码'0xAB56'即可发生高级软件复位;

特别地、Flash 配置区中对配置字进行修改的操作需要产生一次 POR 复位或者高级软件复位,更多信息请参考"16.3.5 配置区操作"。

### 4.4 时钟功能描述

三种不同的时钟源可被用来驱动系统时钟(SYS CLK):

- HSI 振荡器时钟

- PLL 时钟

- LSI 振荡器时钟

当不被使用时,任一个时钟源都可被独立地启动或关闭,以优化系统功耗。

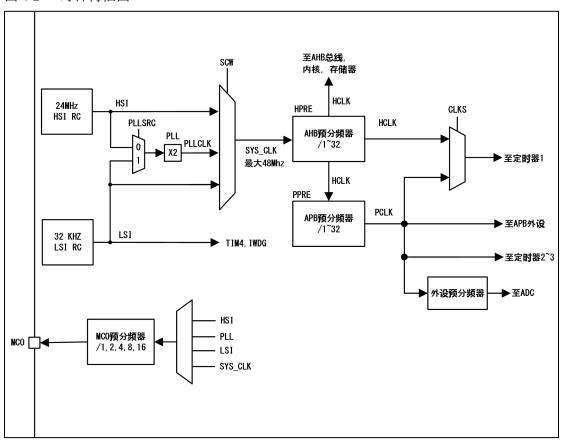

图 4-2 时钟树框图

- 1. 当 HSI 被用于作为 PLL 时钟的输入时,系统时钟 SYS\_CLK 即得到最大频率 48Mhz。

- 2. 对于时钟源的更多特性,请参考相应产品《PT32x00x数据手册》中"电气特性"章节。

- 3. 用户可通过多个预分频器配置 HCLK、PCLK 的频率。 HCLK 和 PCLK 时钟的最大频率是 48Mhz;

- 4. RCC 通过 HCLK 作为 Cortex M0 系统定时器(SysTick)的外部时钟。

- 5. 外设时钟均由对应的外设分频器生成

### 4.4.1 HSI 时钟

HSI 时钟能够在不需要任何外部器件的条件下提供系统时钟,HSI 时钟信号由内部 24Mhz 的 RC 振荡器产生,可直接作为系统时钟 SYS\_CLK 或者作为 PLL 时钟的输入时钟源。

HSI 在满足时钟安全机制的前提下,可以通过时钟高频控制寄存器 RCC\_HCR 里的 HSIEN 位来使能或禁用,详见时钟安全机制;

注意: HSI 时钟上电默认启用并作为系统时钟源 SYS\_CLK, 直到系统运行、SYS\_CLK 才按照用户配置进行设置。

### 4.4.2 LSI 时钟

LSI 时钟信号由内部 32Khz 的 RC 振荡器产生,同样可以直接作为系统时钟或者作为 PLL 时钟的输入时钟源。

LSI 作为一个低功耗的时钟源,它可以在睡眠或深度睡眠模式下保持运行,为独立看门 狗和自动唤醒定时器 TIM4 提供时钟。

LSI 时钟上电默认启用、在满足时钟安全机制的前提下,可以通过时钟低频控制寄存器 RCC LCR 里的 LSIEN 位来使能或禁用,详见时钟安全机制。

注意: 上电后, LSI 不应该被立刻关闭, 应保证上电后至少 1mS 的延时才能够关闭 LSI。

### 4.4.3 PLL 时钟

内部 PLL 可以用来倍频 HSI RC 的输出时钟或 LSI RC 的输出时钟。参考图 4-2 和(时钟配置寄存器 RCC\_CFGR)。

PLL 的配置(选择 HSI 或 LSI 作为 PLL 的输入时钟源、并选择 PLL 作为系统时钟)必须在其被激活前完成。一旦 PLL 被激活,这些参数就不能被改动。

PLL 时钟的失效将导致(RCC\_CFGR 寄存器)内的 PLL 时钟失效标志位 PLLF 被硬件置'1';此时、如果(RCC\_RCR 寄存器)中的"PREN"位被置'1'、将发生系统复位、从(RCC\_RSR 寄存器)中的"PLLR"位可获取 PLL 导致的系统复位信息。

### 4.4.4 系统时钟(SYS\_CLK)选择

系统复位后, HSI 被选为系统时钟。

当时钟源被直接或者通过 PLL 间接作为系统时钟时,该时钟源将不能被停止。

只有当目标时钟源准备就绪了(经过启动稳定阶段的延迟或 PLL 稳定),系统时钟从一个时钟源切换到另一个时钟源才能够发生;

在被选择时钟源没有就绪时,系统时钟的切换不会发生。直至目标时钟源就绪,才发生切换。

可以通过(RCC\_CFGR 寄存器)里的"SCW"位获取或配置当前系统时钟的时钟源信息。

注意:睡眠唤醒后、系统时钟默认为"睡眠前的时钟配置",可将(RCC\_CFGR 寄存器)的"WKSCK"位清'0'以将时钟自动切换到HSI。

### 4.4.5 时钟安全机制

默认激活的内部时钟安全机制保证即使极端恶劣工况下,芯片也能正常工作:

- 芯片从低功耗模式回到运行模式后,默认系统时钟均为上一次运行模式下的时钟。

- 当时钟源被直接或者通过 PLL 间接作为系统时钟时,该时钟源将不能被停止。

- PLL 时钟失效将导致系统时钟自动切换到 HSI 时钟, PLL 也将被关闭;

- PLL 时钟失效且使能了 PLL 失效复位、在复位动作之后、系统时钟将自动切换到 HSI 时钟。

注意: 当使用PLL 时钟作为系统主时钟进入休眠时,时钟安全机制仍在睡眠下仍作用,且带来了额外的功耗; 为避免额外的睡眠消耗, 应该在睡眠前首先将PLL 时钟切换到HSI 时钟运行。

### 4.4.6 看门狗时钟

如果启用 IWDG, LSI 时钟则不可被关闭,关闭 LSI 时钟将导致 IWDG 不可用。

### 4.4.7 TIM4 时钟

如果启用 TIM4, LSI 时钟则不可被关闭,关闭 LSI 时钟将导致 TIM4 不可用。

# 4.4.8 时钟输出(MCO)

微控制器允许输出时钟信号到外部的 MCO 引脚上。

使用 MCO 功能,对应的 GPIO 端口必须被正确的复用为 MCO 功能。以下四个时钟信号可被选作 MCO 时钟,下列是 MCO 输出时钟源的选择:

- HSI

- PLL

- LSI

- 当前系统时钟

MCO 输出的时钟选择由(时钟输出配置寄存器 RCC\_MCOR)中的"COSRC"位配置, (RCC\_MCOR 寄存器)中的"COPRE"位则用于配置 MCO 输出的时钟信号分频数;

注意: MCO 输出信号频率不应大于 10Mhz, 否则输出信号将产生非预期的畸变。

# 4.5 RCC 寄存器描述

# 4.5.1 时钟高频控制寄存器(RCC\_HCR)

(地址: 0x4000 1810)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| 位域  | -   | -   | ı   | ı   | ı   | ı   | ı   | ı   | ı   | ı   | ı   | ı   | ı   | ı   | ı   | HSIEN |

| R/W | Res | RW    |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1     |

|         | HSIEN: 内部高速时钟使能(HSI enable) |

|---------|-----------------------------|

| 位 0     | 0: HSI 振荡器禁用                |

|         | 1: HSI 振荡器使能                |

| 位 31: 1 | 保留。必须保持为 0。                 |

# 4.5.2 时钟低频控制寄存器(RCC\_LCR)

(地址: 0x4000 1814)

|     |     |     |     | _   |     |     |     |     |     |     |     |     |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | LSIEN |

| R/W | Res | RW    |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1     |

|         | LSIEN:内部低速时钟使能(LSI enable)                       |

|---------|--------------------------------------------------|

| 位 0     | 0: LSI 振荡器禁用                                     |

| 12. V   | 1: LSI 振荡器使能                                     |

|         | 注:上电时,LSI 不应该被立刻关闭,如需优化功率以关闭 LSI,应参考数据手册,保证足够的延时 |

| 位 31: 1 | 保留。必须保持为 0。                                      |

# 4.5.3 时钟 PLL 控制寄存器(RCC\_PCR)

(地址: 0x4000\_1818)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | PLL |

| 世典  | -   | -   | -   | -   | -   | _   | •   | -   | -   | _   | -   | •   | -   | _   | •   | EN  |

| R/W | Res | RW  |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|         | PLLEN: PLL 时钟使能(PLL enable) |

|---------|-----------------------------|

| 位 0     | O: PLL 时钟禁用                 |

|         | 1: PLL 时钟使能                 |

| 位 31: 1 | 保留。必须保持为 0。                 |

# 4.5.4 时钟输出配置寄存器(RCC\_MCOR)

(地址: 0x4000\_1824)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5    | 4      | 3   | 2  | 1     | 0    |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|--------|-----|----|-------|------|

| 位域  | -   | -   | -   | 1   | -   | -   | -   | -   | 1   | -   | COSR | C[1:0] | -   | CC | PRE[2 | 2:0] |

| R/W | Res | RW   | RW     | Res | RW | RW    | RW   |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0      | 0   | 0  | 0     | 0    |

|         | COPRE[2:0]: 时钟输出预分频器(clock output prescaler) |

|---------|----------------------------------------------|

|         | 000: 时钟输出不分频                                 |

|         | 001: 时钟输出 2 分频                               |

| 位 2: 0  | 010: 时钟输出 4 分频                               |

|         | 011: 时钟输出 8 分频                               |

|         | 100: 时钟输出 16 分频                              |

|         | 其他: 无效                                       |

| 位 3     | 保留。必须保持为0。                                   |

|         | COSRC[1:0]: 时钟输出源配置(clock output source)     |

|         | 00: 时钟输出源为 HSI 时钟                            |

| 位 5: 4  | 01: 时钟输出源为 PLL 时钟                            |

|         | 10: 时钟输出源为 LSI 时钟                            |

|         | 11: 时钟输出源为当前系统时钟                             |

| 位 31: 6 | 保留。必须保持为0。                                   |

# 4.5.5 时钟配置寄存器(RCC\_CFGR)

(地址: 0x4001 F00C)

| 位   | 31  | 30  | 29  | 28 | 27          | 26      | 25 | 24 | 23 | 22  | 21  | 20   | 19  | 18  | 17  | 16     |

|-----|-----|-----|-----|----|-------------|---------|----|----|----|-----|-----|------|-----|-----|-----|--------|

| 位域  | -   | -   | -   |    | P           | PRE[4:0 | 0] |    | 1  | -   | -   | WKCK | -   | -   | WKD | L[1:0] |

| R/W | Res | Res | Res | RW | RW RW RW RW |         |    |    |    | Res | Res | RW   | Res | Res | RW  | RW     |

| 复位  | 0   | 0   | 0   | 0  | 0           | 0       | 0  | 0  | 0  | 0   | 0   | 1    | 0   | 0   | 0   | 0      |

| 位   | 15   | 14  | 13  | 12  | 11  | 10  | 9   | 8  | 7  | 6       | 5  | 4  | 3   | 2          | 1   | 0     |

|-----|------|-----|-----|-----|-----|-----|-----|----|----|---------|----|----|-----|------------|-----|-------|

| 位域  | PLLF | -   | -   | -   | -   | -   | -   |    | Н  | PRE[4:0 | 0] |    | -   | PLL<br>SRC | SCW | [1:0] |

| R/W | RW   | Res | Res | Res | Res | Res | Res | RW | RW | RW      | RW | RW | Res | RW         | RW  | RW    |

| 复位  | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0       | 0  | 0  | 0   | 0          | 0   | 0     |

|          | SCW: 系统时钟切换(system clock switch)             |

|----------|----------------------------------------------|

| 位1:0     | 0x: HSI 振荡器作为系统时钟                            |

| <u> </u> | 10: PLL 时钟作为系统时钟                             |

|          | 11: LSI 振荡器作为系统时钟                            |

|          | PLLSRC: PLL 输入时钟源 (PLL entry clock source)   |

| 位 2      | 0: HSI 振荡器作为 PLL 输入时钟源                       |

|          | 1: LSI 时钟作为 PLL 输入时钟源                        |

| 位 3      | 保留。必须保持为 0。                                  |

|          | HPRE[4:0]: HCLK 预分频(HCLK prescaler)          |

|          | 00000: HCLK 不分频                              |

|          | 00001: HCLK 2 分频                             |

| 位 8: 4   | 00010: HCLK 3 分频                             |

|          |                                              |

|          | 11110: HCLK 31 分频                            |

|          | 11111: HCLK 32 分频                            |

| 位 14: 9  | 保留。必须保持为 0。                                  |

|          | PLLF: PLL 时钟失效标志位(PLL fail flag)             |

| 位 15     | 0: 无 PLL 时钟失效发生                              |

|          | 1: 发生 PLL 时钟失效                               |

|          | WKDL[1:0]: 唤醒延时时间(wake up delay times)       |

|          | 00: 最大延时, 320 个 SYS_CLK 时钟周期                 |

| 位 17: 16 | 01: 次大延时, 160 个 SYS_CLK 时钟周期                 |

| <u> </u> | 10: 次小延时, 132 个 SYS_CLK 时钟周期                 |

|          | 11: 最小延时, 96 个 SYS_CLK 时钟周期                  |

|          | 注: 详见电源控制一节 3.4.5 唤醒时间描述                     |

| 位 19: 18 | 保留。必须保持为 0。                                  |

| 位 20     | WKSK: 唤醒后默认系统时钟配置(system clock after wakeup) |

## PT32x00x 参考手册

|          | 0: 系统时钟默认为 HSI 时钟                   |

|----------|-------------------------------------|

|          | 1: 系统时钟默认为睡眠之前的系统时钟                 |

| 位 23: 21 | 保留。必须保持为 0。                         |

|          | PPRE[4:0]: PCLK 预分频(PCLK prescaler) |

|          | 00000: PCLK 不分频                     |

|          | 00001: PCLK 2 分频                    |

| 位 28: 24 | 00010: PCLK 3 分频                    |

|          |                                     |

|          | 11110: PCLK 31 分频                   |

|          | 11111: PCLK 32 分频                   |

| 位 31: 29 | 保留。必须保持为 0。                         |

# 4.5.6 复位状态寄存器 RCC\_RSR

(地址: 0x4001\_F010)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8    | 7    | 6   | 5    | 4   | 3   | 2   | 1     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|------|------|-----|------|-----|-----|-----|-------|-----|

| 位域  | 1   | ı   | -   | ı   | -   | 1   | -   | PVDR | PINR | POR | PLLR | -   | 1   | -   | IWDGR | SFR |

| R/W | Res | Rw1  | Rw1  | Rw1 | Rw1  | Res | Res | Res | Rw1   | Rw1 |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0   | 0    | 0   | 0   | 0   | 0     | 0   |

|         | SFR: 软件复位标志(software reset)            |

|---------|----------------------------------------|

| 位 0     | 0: 无软件复位发生                             |

|         | 1: 发生软件复位,该位写 1 清除                     |

|         | IWDGR: 独立看门狗复位标志(iwdg reset)           |

| 位 1     | 0: 无独立看门狗复位发生                          |

|         | 1: 发生独立看门狗复位,该位写 1 清除                  |

| 位 4: 2  | 保留。必须保持为0。                             |

|         | PLLR: PLL 时钟失效复位标志(PLL fail reset)     |

| 位 5     | 0: 无 PLL 时钟失效复位发生                      |

|         | 1: 发生 PLL 时钟失效复位,该位写 1 清除              |

|         | POR: 上电/掉电复位标志(power reset)            |

| 位 6     | 0: 无上电/掉电复位发生                          |

|         | 1: 发生上电/掉电复位,该位写 1 清除                  |

|         | PINR: NRST 引脚复位标志(pin reset)           |

| 位 7     | 0: 无 NRST 引脚复位发生                       |

|         | 1: 发生 NRST 引脚复位,该位写 1 清除               |

|         | PVDR: 电源低电压复位标志(PVD low voltage reset) |

| 位 8     | 0: 无电源低电压复位发生                          |

|         | 1: 发生电源低电压复位,该位写 1 清除                  |

| 位 31: 9 | 保留。必须保持为 0。                            |

# 4.5.7 高级软件复位控制寄存器(RCC\_HSFRR)

(地址: 0x4001\_F014)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15        | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|-----------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 位域  | Key[15:0] |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| R/W | W         | W  | W  | W  | W  | W  | W | W | W | W | W | W | W | W | W | W |

| 复位  | 0         | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|                                               | Key[15:0]: 高级软件复位密码(key)                      |

|-----------------------------------------------|-----------------------------------------------|

| 位 15: 0                                       | 0xAB56: 写入密码、发生高级软件复位                         |

| <u>                                      </u> | 其他值: 无效                                       |

|                                               | 注:只有当(RCC_RCR 寄存器)的"HREN"位被使能时,写入密码才能发生高级软件复位 |

| 位 31: 0                                       | 保留。必须保持为 0。                                   |

# 4.5.8 复位控制寄存器 RCC\_RCR

(地址: 0x4001\_F018)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15  | 14  | 13  | 12  | 11  | 10   | 9   | 8    | 7   | 6   | 5    | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|------|-----|------|-----|-----|------|-----|-----|-----|-----|-----|

| 位域  | -   | 1   | -   | -   | -   | HREN | -   | PDRE | -   | -   | PREN | -   | ı   | -   | ı   | -   |

| R/W | Res | Res | Res | Res | Res | RW   | Res | RW   | Res | Res | RW   | Res | Res | Res | Res | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0    | 1   | 1    | 0   | 1   | 0    | 0   | 0   | 0   | 0   | 0   |

| 位 4: 0   | 保留。必须保持为 0。                                       |

|----------|---------------------------------------------------|

|          | PREN: PLL 时钟失效复位使能(PLL fail reset enable)         |

| 位 5      | 0: 复位禁止                                           |

|          | 1: 复位使能                                           |

| 位 7: 6   | 保留。必须保持为 0。                                       |

|          | PDRE: 电源低电压检测触发复位使能(PVD low voltage reset enable) |

| 位 8      | 0: 复位禁止                                           |

|          | 1: 复位使能                                           |

| 位 9      | 保留。必须保持为 0。                                       |

|          | HREN: 高级软件复位使能(Advanced software reset enable)    |

| 位 10     | 0: 复位禁止                                           |

|          | 1: 复位使能                                           |

| 位 31: 11 | 保留。必须保持为 0。                                       |

# PT32x00x 参考手册

# 4.5.9 寄存器列表

| 地址          | 寄存器       | 描述           | 备注           |

|-------------|-----------|--------------|--------------|

| 0x4000_1810 | RCC_HCR   | 时钟高频控制寄存器    | RCC_HCR 说明   |

| 0x4000_1814 | RCC_LCR   | 时钟低频控制寄存器    | RCC_LCR 说明   |

| 0x4000_1818 | RCC_PCR   | 时钟 PLL 控制寄存器 | RCC_PCR 说明   |

| 0x4000_1824 | RCC_MCOR  | 时钟输出配置寄存器    | RCC_MCOR 说明  |

| 0x4001_F00C | RCC_CFGR  | 时钟配置寄存器      | RCC_CFGR 说明  |

| 0x4001_F010 | RCC_RSR   | 复位状态寄存器      | RCC_RSR 说明   |

| 0x4001_F014 | RCC_HSFRR | 高级软件复位控制寄存器  | RCC_HSFRR 说明 |

| 0x4001_F018 | RCC_RCR   | 复位控制寄存器      | RCC_RCR 说明   |

# 5 通用和复用功能 I/O(GPIO 和 AFIO)

### 5.1 综述

根据《PT32x00x 数据手册》中列出的每个 I/O 引脚和相关的硬件特征,每个 I/O 都可以由软件分别配置、按照输入输出模式可以有如下配置:

- 输入:

- 输入浮空

- 输入上拉

- 输入下拉

- 数字复用输入

- 模拟复用输入

- 输出

- 开漏输出

- 开漏弱上拉/下拉输出

- 推挽输出

- 数字复用输出

- 模拟复用输出

每个 I/O 可以被自由编程, 然而 I/O 相关寄存器必须按 32 位字访问(不可以半字或字节访问)。

### 5.2 特征

- 所有的 I/0 都可配置为输入或输出

- 所有的 I/0 都可作为外部中断

- 可选的、多功能的数字功能复用

- 可选的、多功能的模拟功能复用

- 通过分开的使能和失能操作控制寄存器,提供中断安全的 GPIO 操作

- 提供内部弱上/下拉电阻,上/下拉电阻阻值详见《PT32x00x 数据手册》

- 端口映射操作,提供单指令的 I/O 操作,以保障中断安全

### 5.3 GPIO/AFIO 功能描述

复位期间和刚复位后,除 SWD 接口和 NRST 引脚外、所有的 I/O 默认为输入浮空 (GPIOx\_OES 寄存器的 "IOy"=0, GPIOx\_PUS 寄存器的 "IOy"=0, GPIOx\_PDS 寄存器的 "IOy"=0), 直到进入运行模式,用户对 I/O 的配置才能够生效;

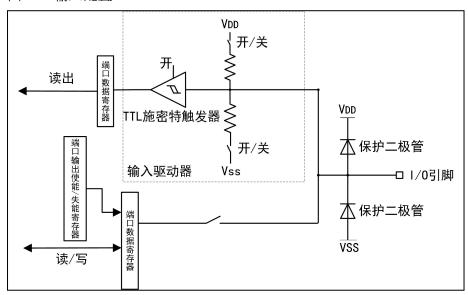

### 5.3.1 GPIO 输入配置

GPIO 上电默认输入:

配置 GPIO 为输出后,通过将(端口输出失能寄存器 GPIOx\_OEC)的相关位置'1'以清除 GPIO 输出配置,并将 GPIO 恢复到输入模式;

当 GPIO 被配置为输入时:

- 输出驱动器被禁止

- 根据输入配置(上拉、下拉、施密特触发)的不同,弱上拉/下拉电阻和施密特触发器被连接

- 出现在 I/O 脚上的数据在每个 HCLK 时钟被采样到(端口数据寄存器 GPIOx\_DR)

- 对(GPIOx\_DR 寄存器)的读访问可得到当前 I/O 状态

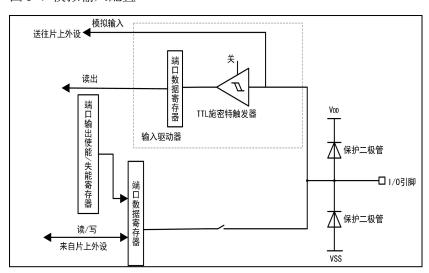

#### 图 5-1 输入配置

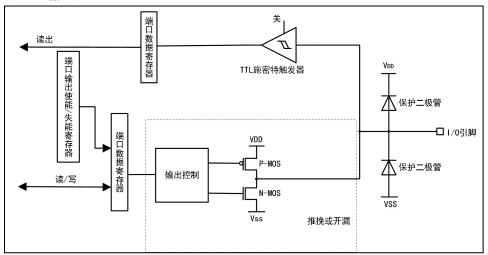

### 5.3.2 GPIO 输出配置

通过将(端口输出使能寄存器 GPIOx\_OES)的相关位置'1'以将 GPIO 配置为输出模式; 当 GPIO 被配置为输出时:

- 输出驱动器被开启

- 输出配置

- 1. 开漏模式: (GPIOx\_DR 寄存器)上的'0'开启 N-MOS,而(GPIOx\_DR 寄存器) 上的'1'将端口置于高阻状态(PMOS 从不被开启)。

- 2. 推挽模式: (GPIOx\_DR 寄存器)上的'0'开启 N-MOS,而(GPIOx\_DR 寄存器) 上的'1'将开启 P-MOS。

- 在推挽模式下、弱上拉/下拉电阻被禁止

- 出现在 I/O 脚上的数据在每个 HCLK 时钟被采样到(GPIOx\_DR 寄存器)

- 对(GPIOx\_DR 寄存器)的读访问可得到当前 I/O 状态

下图给出了 I/O 端口位的输出配置。

图 5-2 输出配置

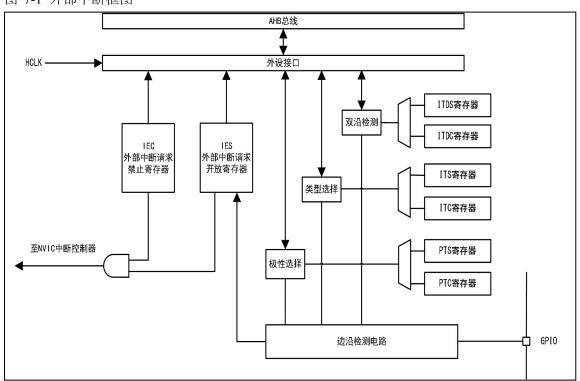

### 5.3.3 外部中断

所有 I/O 都有外部中断能力。为了使用外部中断,端口必须配置成输入模式。 更多的关于外部中断的信息,请参考: "外部中断控制器(EXTI)"一章

### 5.3.4 映射操作

通过(GPIO\_DR 寄存器)对 I/O 操作时,由于寄存器的操作是按'字'进行的,为了避免对其他 I/O 的误操作,一般流程如下:

- 读 DR 寄存器

- DR 寄存器值与目标 I/O 的值进行'逻辑与'I'逻辑或'操作

- 操作结果赋值给 DR 寄存器

在一些 I/O 模拟并行总线或需要快速切换 I/O 的应用场合,上述流程的执行可能导致无法满足速率要求:

PT 提供了一种映射操作,这种操作有:

- 对 x 端口内的单个或多个 I/O 的操作是绝对的(这意味着 x 端口内的其他 I/O 不会被影响)

- 鉴于其操作的"绝对"特性,可以直接赋值,保障了中断安全。

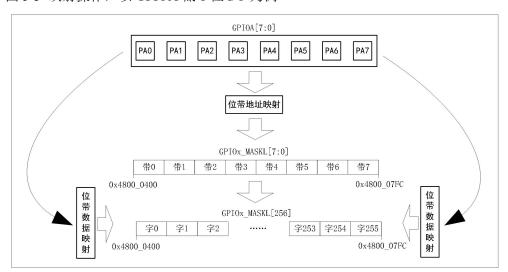

图 5-3 映射操作,以 GPIOA 低 8位 I/O 为例

对于 16 位宽的一个端口 GPIOx[15:0],映射操作分低 8 位和高 8 位两组进行,分别映射至 GPIOx\_MASKL[7:0]和 GPIOx\_MASKH[7:0]。

示例: 需要 PAO 和 PA1 输出高, PA6 和 PA7 输出低,不改变端口内的其他 I/O。

- 参考图 5-3 的位带"地址"映射,确定所需操作的 I/O 位于"带 0、1、6、7",用二进制表示为"11000011",故可以确定目标地址为 GPIOx\_MASKL[0xC3],该地址是绝对的,只对应 PA0、PA1、PA6 和 PA7,对 GPIOA 端口内的其他 I/O 是无意义的。

- 参考图 5-3 的位带"数据"映射, 我们需要 PAO 和 PA1 输出高,则 GPIOA[1:0]=11,GPIOA[7:6]=00,用二进制表示为"00xxxx11(x 代表 0 或 1 任意值)",最终,地址 GPIOx\_MASKL[0xC3]=0x03,即一次实现了四个数据位同步置1和清零的操作。

#### 注意:

- 1. 使用映射操作前,相关 I/O 应当被配置为输出模式

- 2. GPIOx MASKL[7:0]和GPIOx MASKH[7:0]地址,仅低8位有意义。

### 5.3.5 AFIO 复用 IO 功能功能描述

引脚是有限的,但功能却可以是多样的;

PT 为 GPIO 提供了多种功能,这些功能可以分为数字功能和模拟功能,通过对引脚功能的灵活配置,可以满足更多样化的需求。

复位期间和刚复位后,除必须的功能(SWD、可能的 NRST)外,所有的 GPIO 默认为主功能,直到进入运行模式,用户对引脚的复用才能够生效;

注意: 关于IO 引脚支持的复用功能、请参考《PT32x00x 数据手册》中的引脚定义部分。

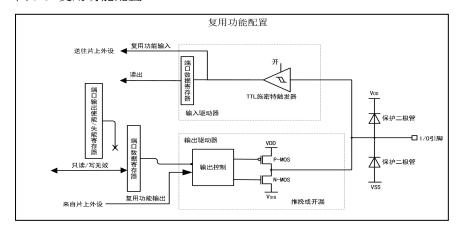

#### 5.3.5.1 数字功能复用配置

数字功能输入输出均为数字信号:

端口数字功能配置寄存器(AFIOx\_AFS0)和(AFIOx\_AFS1)用于配置 GPIO 的数字复用功能,每个 GPIO 引脚都有独立的 3bit 位宽的配置位,它最多支持 GPIO 引脚复用 7个数字功能,详见(AFIOx AFS0)或(AFIOx AFS1)寄存器的说明。

端口复用功能清除寄存器(AFIOx\_AFC)用于清除相应的 GPIO 引脚复用功能、以将相应的 GPIO 引脚功能恢复到主功能:

当 I/O 端口被复用为数字功能时:

- I/O 的输入输出模式内部自动配置

- 手动启用的施密特触发输入

- 手动启用的弱上拉和弱下拉电阻

- 在每个 HCLK 时钟周期,出现在 I/O 脚上的数据被采样到(GPIOx DR 寄存器)

- 开漏模式下,读(GPIOx\_DR 寄存器)可以得到 I/O 口状态

- 在推挽模式时,读(GPIOx\_DR 寄存器)可以得到当前 I/O 状态

当资源允许,用户可以把一些复用功能重新映射到不同的引脚(参考《PT32x00x 数据手册》中的引脚定义部分),下图展示了 I/O 端口位的复用功能配置。

#### 注意:

- 1. 一个 GPIO 引脚可能支持多种数字功能和模拟功能,但同一时间内、GPIO 引脚只能使用其中一种,禁止将模拟功能和数字功能混用。

- 2. 切换不同的数字复用功能前,必须在(GPIOx AFC)中先将之前的复用清除。

图 5-3 复用功能配置

#### 5.3.5.2 模拟功能复用配置

模拟功能的输入输出均为模拟信号;

(端口模拟功能使能寄存器 ANAS)和(端口模拟功能失能寄存器 ANAC)用于管理 GPIO 的模拟复用功能;

当 GPIO 的模拟复用功能被使能后,只有相关的模块(如 ADC)被正确配置, GPIO 的模拟功能才能正常使用;

当 I/O 端口被配置为模拟输入配置时:

- 输出缓冲器被禁止;

- 弱上拉和下拉电阻被禁止;

- 读取(GPIOx\_DR 寄存器)时数值为'0'。

下图示出了 I/O 端口的模拟输入配置:

注意:一个GPIO 引脚可能支持多种模拟功能,但同一时间内、只能开启一个模拟功能, 否则将导致功能异常。

图 5-4 模拟输入配置

(1)模拟复用输入模式仅在集成了 ADC 外设、OPA 外设、CMP 外设的产品上有效

(2)模拟复用输出模式仅在集成了 DAC 外设、LCD 外设、OPA 外设、CMP 外设的产品上有效

# 5.3.6 外设复用下的 IO 状态

下列表格列出了各个外设的引脚配置。

#### 表 5-1 高级定时器 TIM1

| TIM1 引脚   | 配置       | IO 状态 |

|-----------|----------|-------|

| TIM1 CIL. | 输入捕获通道 x | 浮空输入  |

| TIM1_CHx  | 输出比较通道 x | 推挽输出  |

| TIM1_CHxN | 互补输出通道 x | 推挽输出  |

| TIM1_BKIN | 刹车输入     | 浮空输入  |

#### 表 5-2 UART

| UART 引脚  | 配置      | IO 状态         |

|----------|---------|---------------|

|          | 全双工模式   | 推挽输出          |

| UARTx_TX | 单线半双工模式 | 推挽输出/浮空输入     |

|          | 单线单工模式  | 推挽输出          |

|          | 全双工模式   | 浮空输入          |

| UARTx_RX | 单线半双工模式 | 推挽输出          |

|          | 单线单工模式  | 未使用,可作为通用 I/O |

#### 表 5-3 SPI

| SPI 引脚   | 配置    | IO 状态         |

|----------|-------|---------------|

| CDL CCV  | 主模式   | 推挽输出          |

| SPI_SCK  | 从模式   | 浮空输入          |

| CDI MOCI | 主模式   | 推挽输出          |

| SPI_MOSI | 从模式   | 浮空输入          |

| CDI MICO | 主模式   | 浮空输入          |

| SPI_MISO | 从模式   | 推挽输出          |

|          | 硬件主模式 | 推挽输出          |

| SPI_CS   | 硬件从模式 | 浮空输入          |

|          | 软件模式  | 未使用,可作为通用 I/O |

### 表 5-4 I2C

| I2C 引脚  | 配置     | IO 状态 |

|---------|--------|-------|

| I2C_SCL | I2C 时钟 | 开漏输出  |

| I2C_SDA | I2C 数据 | 开漏输出  |

#### 表 5-5 ADC

| I2C 引脚  | 配置       | IO 状态 |

|---------|----------|-------|

| ADC_INx | ADC 输入通道 | 模拟输入  |

### 表 5-6 其他 I/O 功能

| 引脚  | 描述     | IO 状态 |

|-----|--------|-------|

| MCO | 系统时钟输出 | 推挽输出  |

## 5.4 GPIO 寄存器描述

请参考第 1 章中用到的缩写。 必须以字(32 位)的方式操作这些外设寄存器。

# 5.4.1 端口数据寄存器(GPIOx\_DR) (x=A..D)

(地址: GPIOA: 0x4800\_0000; GPIOB: 0x4800\_1000; GPIOC: 0x4800\_2000; GPIOD: 0x4800\_3000)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W | Res |

| 复位  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| 位   | 15   | 14   | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | DR15 | DR14 | DR13 | DR12 | DR11 | DR10 | DR9 | DR8 | DR7 | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |

| R/W | RW   | RW   | RW   | RW   | RW   | RW   | RW  | RW  | RW  | RW  | RW  | RW  | RW  | RW  | RW  | RW  |

| 复位  | 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|          | DRy: 端口 x 引脚 y 的输入/输出数据(port x pin y data) |

|----------|--------------------------------------------|

| 位 15: 0  | 0: 端口 x 引脚 y 输入/输出为低电平                     |

|          | 1: 端口 x 引脚 y 输入/输出为高电平                     |

| 位 31: 16 | 保留,必须保持为 <b>0</b> 。                        |

# 5.4.2 端口输出使能寄存器(GPIOx\_OES) (x=A..D)

(地址: GPIOA: 0x4800\_0008; GPIOB: 0x4800\_1008; GPIOC: 0x4800\_2008; GPIOD: 0x4800\_3008)

| 位   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 位域  | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   | -   |

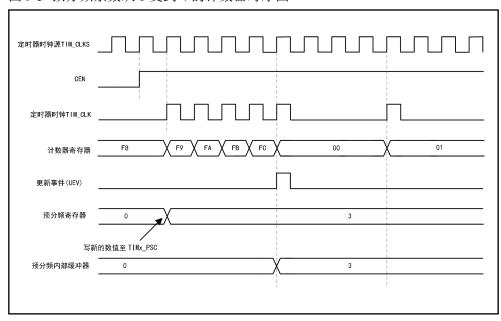

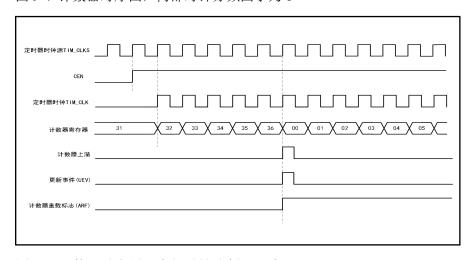

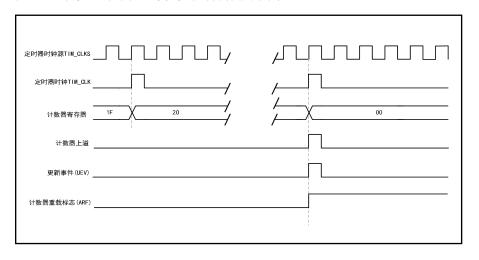

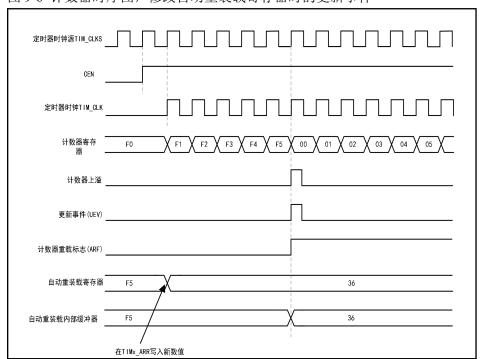

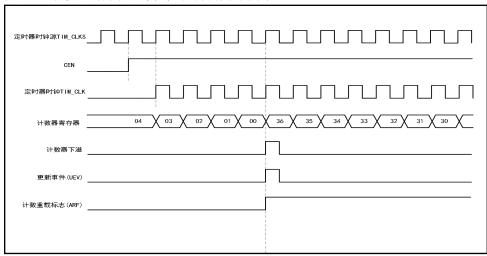

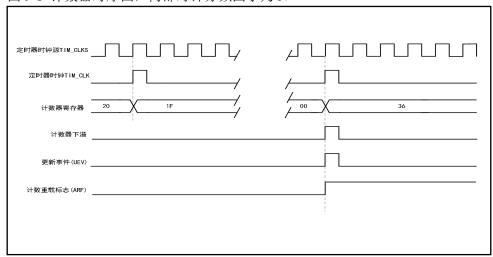

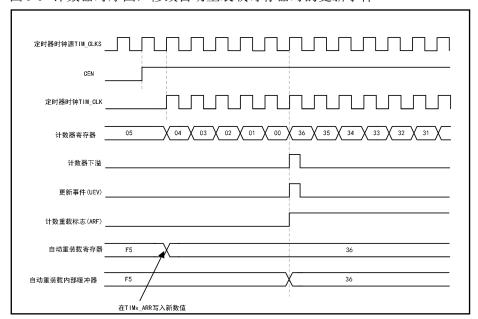

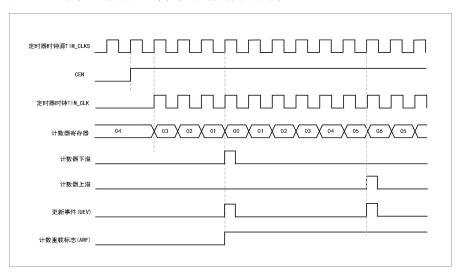

| R/W | Res |